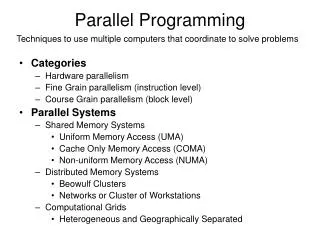

Visualization of Parallel Programming

This project focuses on visualizing parallel programming using a tool developed to enhance understanding of message passing in parallel systems. The implementation utilizes an Intel® Quad-Core Processor to compute the sum of the first 100 integers, both sequentially and in parallel across multiple processors. Key components include architecture diagrams, a demonstration of parallel execution, and an exploration of the advantages and challenges of parallel processing. Future work includes extending functionality and refining the tool for classroom testing.

Visualization of Parallel Programming

E N D

Presentation Transcript

Visualization of Parallel Programming A Tool for Understanding Message Passing in Parallel Systems Andrew Schwartz ‘13 Computer Science Union College Advisor: Professor Barr

Introduction Intel® Quad Core Processor “Supercomputer”

Sum (Single Processor) Sum first 100 integers Processor Input Output 1 x=5050 1-100 x=1 x=x+2 x=x+3 … x=x+100 100 additions

Sum (5 Processors) 1-20 x1= 210 1 xtotal=x1+x2 xtotal= xtotal+x3 xtotal= xtotal+x4 xtotal= xtotal+x5 21-40 x2= 610 2 Input x3= 1010 Output 41-60 3 1-100 xtotal=5050 x4= 1410 61-80 4 100+ 4 additions First step parallelized x5= 1810 5 81-100

Timeline Analysis Single processor P0 (100 additions = 100 time steps) 100 0 Time Five processors P5 P0 100 24 0 20 Time (104 additions, but ~24 time steps

Architecture Diagrams NUMA Architecture Courtesy: Florida State University goparallel.sourceforge.ne

Background Options limited Needs more information! NEXT!

Background MPICL/ParaGraph Overview • “Installation a nightmare” • Dozens of views and diagrams OVERKILL

Future Work Core design challenges met QoL functionality still left to be implemented before release Extensible project design -> new functions can be modeled with new algos Port to UNIX via Mono Initial results promising but need to test in the classroom