Universal Logic Restructuring: Irredundancy Removal and Addition

Explore circuit rewiring techniques for removing unnecessary wires and gates, with innovative ATPG-based and ATPG/Diagnosis-based approaches. Learn about Mandatory Assignments and Forced MA calculations.

Universal Logic Restructuring: Irredundancy Removal and Addition

E N D

Presentation Transcript

A Universal Logic Restructuring Technique: Irredundancy Removal and Addition Speaker : Chun-ChiLin Advisor : Chun-Yao Wang 2008.07.22

Outline • Introduction • Notations and Background • Proposed approach • Conclusion

Redundancy Addition and Removal • Acircuit rewiringtechnique • The objective is to add someredundant wires/gates such that a given target wire becomes redundant • It will not change the functionality of the circuit

A RAR Example Add redundant wire(g1 → g4) can make wire(c → g2) become redundant a g2 b target wire g1 c o1 d g3 g4 o2 e

ATPG-based RAR approach • Little memory requirement for large circuits • Two-stage algorithm • Build up candidate set for the target wire • Redundancy tests on each candidate wire • One-stage algorithm • Without redundancy tests • The rewiring capability is not as good as two-stage algorithm

ATPG-based RAR approach The capability of alternative wires identification is limited by the Mandatory Assignments (MAs) Multiple wire/gates addition still only considers the gates are the MAs for addition

ATPG/Diagnosis-based Design Rewiring (ADDR) • A rewiring technique using ATPG anddiagnosis • With more rewiring capability • Step1: • Inject a design error first, where the error results in the removal of a target wire • Step2: • Generate test vectors for the error by ATPG

ATPG/Diagnosis-based Design Rewiring (ADDR) • Step3: • Input the original circuit, error circuit, and test vectors. Search the possible corrections for the error using simulation-based Design Error Diagnosis and Correction • Step4: • Verify the circuit after the correction • However, the target wire cannot be removed if no corrections

Problem Formulation • Given: • An arbitrarily target wire in a combinational circuit • Objective: • Remove the target wire, the functionality may change • Rectify the functionality by adding some wire/gates

Outline • Introduction • Notations and Background • Proposed approach • Conclusion

Notations and Background • Controlling value, cv(g) • An input of a gate g has a cv(g) if this value determines the output of g regardless of the other inputs • Non-controlling value, ncv(g) • An input of a gate g has a ncv(g) if this value cannot determine the output of g directly • For example • AND gate has cv 0 and ncv 1

Notations and Background • Dominator • The dominators of a wire w is a set of gates G such that all paths from w to any POs have to pass through all gates in G • Fault propagating inputs • Consider the dominators of a wire w, the inputs of a dominator are the inputs in the transitive fanout of w • Side inputs • Other inputs of a dominator

Notations and Background a g2 b target wire g1 c o1 d g3 o2 g4 e • For example • The dominators of the target wire is {g2, g3, g4} • Side inputs are {a, b, d, e}

Notations and Background • For stuck-at-fault test on a wire w(gs→gd) • Set cv at the source gs to activate the fault effect • Set ncv for all side inputs of w’s dominators to propagate the fault effect • The wire is redundant, if no test vector exists

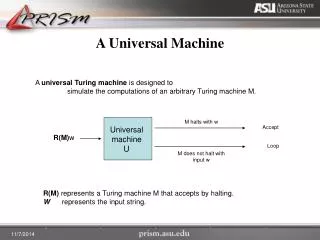

Notations and Background • Mandatory assignments (MAs) • The unique value assignments to gates required for a test to exist • MAs are obtained by • Activating the target fault effect • Setting side inputs of dominators • Implications • Recursive learning can find more MAs

Notations and Background • Forced MA • An MA that causes the target fault untestable while violating it • Forced MAs are obtained by • Activating the fault • Setting side inputs to ncv • Backward implications

Notations and Background g2 1 1 a 1 b g1 c 0 o1 0 d target wire g3 1 0 0/1 g4 o2 e 1 • A MAs Calculation Example • MAs are {g1=0, c=0, d=0, e=1, g3=1, g2=1, a=1, b=1} • These MAs are both forced MAs

Outline • Introduction • Notations and Background • Proposed approach • Conclusion

Opposite direction of RAR • Remove an irredundant wire, then add an other irredundant wire to rectify the functionality of the circuit • This process is called IRredundancy removal and addition (IRRA) a g2 b target wire g1 c o1 d rectification wire g3 g4 o2 e

Source MA (SMA) Given a set of MAs for a target fault, the MA whose transitive fanin cone contains no MAs is a source MA (SMA) The cofactor result with respect to all SMAs is the same as with respect to all MAs

A SMA example g2 1 a b g1 c 0 o1 0 d target wire g3 1 0 0/1 g4 o2 e 1 • MAs are {g1=0, c=0, d=0, e=1, g3=1, g2=1} • SMAs are {c=0, d=0, e=1, g2=1}

Rectification location • Adestination gd is selected from the dominators where the rectification occurs • The differences are the minterms • Changed from 0 to 1 • Changed from 1 to 1 • Two networks are defined to represent these differences

EAN & ERN • Given a Boolean network, a target wire and a destination gate gd in the dominators of the target wire • Exact Addition Network (EAN) at gd is the network having minterms changed from 0 to 1 at gd after removing the target wire • Exact Removal Network (ERN) at gd is the network having minterms changed from 1 to 0 at gd after removing the target wire

EAN & ERN wt g1 a g3 g5 bc b O a 0 1 0 1 g2 c g4 • For example • Suppose the destination gate gd is g5 • EAN is the network composed of abc • ERN is the network composed of abc

EAN & ERN • Supposes the cofactors of gd with respect to SMA in good/faulty circuits are denoted gdg(SMA) and gdf(SMA), respectively • The product of all SMAs is denoted as AND(SMA) • The Boolean function of EAN at gd is • AND(SMA)·gdg(SMA)·gdf(SMA) • The Boolean function of ERN at gd is • AND(SMA)·gdg(SMA)·gdf(SMA)

EAN & ERN wt g1 a 0 g3 g5 1 b O g2 c g4 • For example • gd is g5 • SMAs are {a=0, b=1} • gdg(a=0, b=1)/gdf(a=0, b=1) = c/c • EANat gd =ab·c·c = abc • ERNat gd =ab·c·c = abc

EAN & ERN • The rectification network at gd after removing the target wire is • (gd+ERN)·EAN • All minterms from 1 to 0 will be changed from 0 to 1 after ORing the ERN • All minterms from 0to 1 will be changed from 1 to 0 after ANDing the EAN • (gd+ERN)·EAN = gd·EAN +ERN

EAN & ERN g5 SMAs … gdg(SMA) gdg(SMA) g5 1 1 SMAs g6 … 0 0 1 g1 g2 0 gd redundant redundant 0 0 gdf(SMA) gdf(SMA) 1 EAN ERN gdf(SMA) = 0 g4 1 g3 gdf(SMA) = 1 … • General scheme of the rectification network • the gdf(SMA)part is redundant

EAN & ERN SMAs SMAs … … gdg(SMA) gdg(SMA) gd EAN ERN … • General scheme of the simplified rectification network • EAN at gd is AND(SMA)·gdg(SMA) • ERN at gd is AND(SMA)·gdg(SMA)