Computer Arithmetic

Computer Arithmetic. Chapter 3. Arithmetic. Numbers and number representation Addition and Subtraction Multiplication Division Floating point arithmetic. Numbers and their representation. Representation ASCII - text characters Easy read and write of numbers

Computer Arithmetic

E N D

Presentation Transcript

Computer Arithmetic Chapter 3 Xiaoyu Zhang, CSUSM

Arithmetic • Numbers and number representation • Addition and Subtraction • Multiplication • Division • Floating point arithmetic Xiaoyu Zhang, CSUSM

Numbers and their representation • Representation • ASCII - text characters • Easy read and write of numbers • Complex arithmetic (character wise) • Binary number • Natural form for computers • Requires formatting routines for I/O • in MIPS (32-bit number): • Least significant bit is right (bit 0) • Most significant bit is left (bit 31) Xiaoyu Zhang, CSUSM

Number types • Integer numbers, unsigned • Address calculations • Numbers that can only be positive • Signed numbers • Positive • Negative • Floating point numbers • numeric calculations • Different grades of precision • Singe precision (IEEE) • Double precision (IEEE) Xiaoyu Zhang, CSUSM

Number representations • Bits are just bits (no inherent meaning) • Conventions / contexts define relationship between bits and numbers • Binary numbers (base 2). • E.g. 1011 • Things may become complicated. • Numbers are finite (overflow) • Fraction and real numbers • Negative numbers • How do we represent negative numbers? Xiaoyu Zhang, CSUSM

Possible Representations • Sign and Magnitude • 000 = 0, 001 = 1, 010 = 2, 011 = 3 • 100 = -0, 101 = -1, 110 = -2, 111 = -3 • One’s Complement • 000 = 0, 001 = 1, 010 = 2, 011 = 3 • 100 = -3, 101 = -2, 110 = -1, 111 = -0 • Two’s complement • 000 = 0, 001 = 1, 010 = 2, 011 = 3 • 100 = -4, 101 = -3, 110 = -2, 111 = -1 • How to evaluate? Xiaoyu Zhang, CSUSM

-1 +0 +1 -2 1111 0000 1110 0001 -3 +2 + 1101 0010 -4 +3 1100 0011 0 100 = + 4 -5 1011 +4 1 100 = - 4 0100 1010 0101 -6 +5 - 1001 0110 +6 -7 1000 0111 +7 -8 2's complement Only one representation for 0 One more negative number than positive number Xiaoyu Zhang, CSUSM

MIPS • 32 bit signed numbers:0000 0000 0000 0000 0000 0000 0000 0000two = 0ten0000 0000 0000 0000 0000 0000 0000 0001two = + 1ten0000 0000 0000 0000 0000 0000 0000 0010two = + 2ten...0111 1111 1111 1111 1111 1111 1111 1110two = + 2,147,483,646ten0111 1111 1111 1111 1111 1111 1111 1111two = + 2,147,483,647ten1000 0000 0000 0000 0000 0000 0000 0000two = – 2,147,483,648ten1000 0000 0000 0000 0000 0000 0000 0001two = – 2,147,483,647ten1000 0000 0000 0000 0000 0000 0000 0010two = – 2,147,483,646ten...1111 1111 1111 1111 1111 1111 1111 1101two = – 3ten1111 1111 1111 1111 1111 1111 1111 1110two = – 2ten1111 1111 1111 1111 1111 1111 1111 1111two = – 1ten Xiaoyu Zhang, CSUSM

Working with 2's complements • Negate a number • Invert every single bit (0 > 1, 1 > 0) • Add 1 to the result • Example • 0000 0010 = 2 • 1111 1101 inverted • 1111 1110 1 added = -2 • 0000 0001 inverted • 0000 0010 1 added = 2 Xiaoyu Zhang, CSUSM

Working with 2's complements • Expansione.g. convert 16 bit numbers to 32 bit numbers • Required for operations with registers (32 bits) and immediate operands (16 bits) • Sign extension • Take the lower 16 bits as they are • Copy the highest bit to the remaining 16 bits • 0000 0000 0000 0010 -> 20000 0000 0000 0000 0000 0000 0000 0010 • 1111 1111 1111 1110 -> -21111 1111 1111 1111 1111 1111 1111 1110 Xiaoyu Zhang, CSUSM

Signed vs. Unsigned • Different compare operations required for both number types • Signed integerslt Set on less thanslti Set on less than immediate • Unsigned integersltu Set on less than unsigned sltiu Set on less than immediate unsigned Xiaoyu Zhang, CSUSM

Example • Register $s01111 1111 1111 1111 1111 1111 1111 1111 • Register $s10000 0000 0000 0000 0000 0000 0000 0001 • Operations slt $t0, $s0, $s1 sltu $t1, $s0, $s1 • Results $t0 = 1 -1 < 1 $t1 = 0 4,294,967,295ten > 1ten Xiaoyu Zhang, CSUSM

Addition & Subtraction • Just like in grade school (carry/borrow 1s)0111 0111 0110+ 0110 - 0110 - 0101 • Two's complement operations easy • subtraction using addition of negated numbers 0111 + 1010 • Overflow (result too large for finite computer word): • e.g., adding two n-bit numbers does not yield an n-bit number 0111 + 0001 note that overflow term is somewhat misleading, 1000 it does not mean a carry “overflowed” Xiaoyu Zhang, CSUSM

255 1111 1111 + 1111 1010 250 249 11111 1001 1000 0001 -127 + 1111 1110 -2 0111 1111 +127 Overflow • The sum of two unsigned numbers can exceed any representation • The operation on 2’s complement numbers can exceed any representation Xiaoyu Zhang, CSUSM

Conditions Operation R esult < 0 A + B A > 0 B > 0 > 0 A + B A < 0 B < 0 < 0 A - B A > 0 B < 0 > 0 A - B A < 0 B > 0 Overflow • General overflow conditions of 2’s complement numbers • No overflow when adding a positive and a negative number • No overflow when signs are the same for subtraction • Consider the operations A + B, and A – B • Can overflow occur if B is 0 ? • Can overflow occur if A is 0 ? Xiaoyu Zhang, CSUSM

Examples • Add 3 to 5 and subtract 5 from 3 as 4-bit 2’s complement numbers Xiaoyu Zhang, CSUSM

Overflow • Hardware detection in the ALU • Generation of an exception (interrupt) • Interrupted address is saved for possible resumption • Jump to predefined address based ontype of exception • Correct & return to program • Return to program with error code • Abort program Xiaoyu Zhang, CSUSM

Overflow • Signed integers cause overflow • add • add immediate (addi) • subtract (sub) • Overflow in unsigned integers:not considered as serious in MIPS • add unsigned (addu) • add immediate unsigned (addiu) • Subtract unsigned (subu) • Handle with care! Xiaoyu Zhang, CSUSM

New MIPS instructions • Byte instructions • lbu: load byte unsigned • Loads a byte into the lowest 8 bit of a register • Fills the remaining bits with '0' • lb: load byte (signed) • Loads a byte into the lowest 8 bit of a register • Extends the highest bit into the remaining 24 bits • Set instructions for conditional branches • sltu: set on less than unsigned • Compares unsigned numbers • sltiu: set on less than unsigned immediate Xiaoyu Zhang, CSUSM

Multiplication • More complicated than addition • accomplished via shifting and addition • More time and more space • Let's look at 3 versions based on grade school algorithm 1000 (multiplicand) __x_1001 (multiplier) • See three revisions of the implementation Xiaoyu Zhang, CSUSM

Multiplication • Binary multiplicationMultiplicand * Multiplier1000 * 1001 1000 0000 0000 1000 .Product 1001000 • Look at current bit position of the multiplier • If multiplier is 1 • then add multiplicand • Else add 0 • shift multiplicand to the left by 1 bit Xiaoyu Zhang, CSUSM

Multiplication Version 1 • 32 bits: multiplier • 64 bits: multiplicand, product, ALU Xiaoyu Zhang, CSUSM

Multiplication: Implementation • Check multiplier to determine whether the multiplicand is added to the product register • Left shift the multiplicand register 1 bit • Right shift the multiplier register 1 bit • Very big too slow! • Example 2x3 • Product Multiplier Multiplicand 0000 0000 0011 0000 0010 • 0000 0010 0001 0000 0100 • 0000 0110 0000 0000 1000 • 0000 0110 Xiaoyu Zhang, CSUSM

Second Version • Half of the 64 bits of the multiplicand are always zero! • Real addition is performed only with 32 bits • Least significant bits of the product don't change • Idea: Keep the multiplicand in a register • Shift the product • Shift the multiplier • ALU reduced to 32 bits! Xiaoyu Zhang, CSUSM

Second Version • If multiplier0 = 1, add multiplicand to the left 32 bit of the product register • Shift the product register right 1 bit • Shift the multiplier register right 1 bit • Example Xiaoyu Zhang, CSUSM

Revised 4-bit example • 2 x 3 or 0010 x 0011 Xiaoyu Zhang, CSUSM

Final Version • Further optimization • At the initial state the product register contains only '0' • The lower 32 bits are simply shifted out • Idea: • use these 32 bits for the multiplier and check the lowest bit of the product register • if add & shift or shift only Xiaoyu Zhang, CSUSM

Final Version • If product0 = 1, add multiplicand to the left 32 bit of the product register • Shift the product register right 1 bit Xiaoyu Zhang, CSUSM

Example • 2x3 or 0010 x 0011 Xiaoyu Zhang, CSUSM

Signed Multiplication • Basic approach: • Store the signs of the operands • Convert signed numbers to unsigned numbers (most significant bit (MSB) = 0) • Perform multiplication • If sign bits of operands as equal • sign bit = 0, else • Negate the product Xiaoyu Zhang, CSUSM

Multiply in MIPS • MIPS provides a pair of 32-bit register Hi and Lo to contain the 64-bit product. • It has two multiply instructions mult and multu • Use mflo and mfhi to move values from Hi and Lo registers to general registers • mult and multu: both ignore overflow, up to the software to check. • Example: • mult $t0, $t1; • mflo $t2; • Pseudoinstruction: mul $t2, $t0, $t1; Xiaoyu Zhang, CSUSM

Divide: Paper & Pencil 1001 Quotient Divisor 1000 1001010 Dividend -1000 0010 0101 1010 –1000 10 Remainder (or Modulo result) See how big a number can be subtracted, creating quotient bit on each step Binary => 1 * divisor or 0 * divisor Dividend = Quotient x Divisor + Remainder Remainder < Divisor 3 versions of divide, successive refinement Xiaoyu Zhang, CSUSM

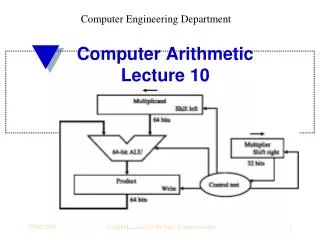

Division Version 1 • 64-bit Divisor reg, 64-bit ALU, 64-bit Remainder reg, 32-bit Quotient reg Shift Right Divisor 64 bits Quotient Shift Left 64-bit ALU 32 bits Write Remainder Control 64 bits Xiaoyu Zhang, CSUSM

Division Version 1 • Each step: • Subtract divisor • Depending on Result • Leave or Restore • Depending on Result • Write '1' or • Write '0‘ to quotient Xiaoyu Zhang, CSUSM

Example • 7/2 or 0000 0111 / 0000 0010 Xiaoyu Zhang, CSUSM

Division V 2 • Similar to multiplication, the division hardware can be improved. • Use 32-bit ALU instead of 64-bit, shift remainder to left • switch order to shift first and then subtract, can save 1 iteration Reduction of Divisor and ALU width by half Xiaoyu Zhang, CSUSM

Improved Division • Similar to multiplication, the division hardware can be improved. • Remainder register keeps quotient. No quotient register required Xiaoyu Zhang, CSUSM

Improved Divide Algorithm • Start by shifting the Remainder left. • Only one shift per loop • The consequence of combining the two registers together and the new order of the operations in the loop is that the remainder will shifted left one time too many. • Thus the final correction step must shift back only the remainder in the left half of the register Xiaoyu Zhang, CSUSM

Example • Well known numbers: 0000 0111 / 0010 Xiaoyu Zhang, CSUSM

Signed division • Keep the signs in mind for Dividend and Remainder • + 7 / + 2 = + 3 Remainder = +1 • 7 = 3 x 2 + (+1) = 6 + 1 • - 7 / + 2 = - 3 Remainder = -1 • -7 = -3 x 2 + (-1) = - 6 - 1 • + 7 / - 2 = - 3 Remainder = +1 • - 7 / - 2 = + 3 Remainder = -1 • One 64 bit register : Hi & Lo • Hi: Remainder, Lo: Quotient • Divide by 0 / overflow : Check by software Xiaoyu Zhang, CSUSM

Divide in MIPS • MIPS uses the Hi and Lo register pair as the 64-bit remainder register • MIPS has two instructions: divide (div), divide unsigned (divu). • Example: • div $t1, $t0; # t1 = 10, t0 = 3; • mflo $t2; • mflh $t3; • What are the values of $t2 and $t3? • Pseudo code: div $t2, $t1, $t0 Xiaoyu Zhang, CSUSM

Floating Point (a brief look) • We need a way to represent • numbers with fractions, e.g., 3.1416 • very small numbers, e.g., .000000001 • very large numbers, e.g., 3.15576 ´ 109 • Representation: • sign, exponent, significand: (–1)sign´ significand ´ 2exponent • more bits for significand gives more accuracy • more bits for exponent increases range • IEEE 754 floating point standard: • single precision: 8 bit exponent, 23 bit significand • double precision: 11 bit exponent, 52 bit significand Xiaoyu Zhang, CSUSM

Floating point numbers • Form • Arbitrary 363.4 • 1034 • Normalized 3.634 • 1036 • Binary notation • Normalized 1.xxx • 2yy • Standard format IEEE 754 • Single precision 8 bit exp, 23 bit significand • 2 • 10 -38 ... 2 • 1038 • Double precision 11 bit exp, 52 bit significand • 2 • 10 -308 ... 2 • 10308 • Both formats are supported by MIPS Xiaoyu Zhang, CSUSM

IEEE 754 floating-point standard • Leading “1” bit of significand is implicit • Saves one bit • Special case: 00…000 represents 0, no leading 1 is added. • Exponent is “biased” to make sorting easier • all 0s is smallest exponent all 1s is largest • bias of 127 for single precision and 1023 for double precision • summary: • (–1)sign× (1+fraction) ×2exponent – bias Xiaoyu Zhang, CSUSM

Example • Show the binary representation of -0.75 in IEEE single precision format • Decimal representation: -0.75 = - 3/4 • Binary representation: - 0.11 = - 1.1 • 2-1 • Floating point • (-1)sign • (1 + fraction) • 2exponent - bias • Sign bit = 1 • Significand = 1 + .1000 .... • Exponent = (-1 + 127) = 126 • 1 01111110 100 0000 0000 0000 0000 0000 • How to represent 5? Xiaoyu Zhang, CSUSM

Floating point Example • What is the value of following IEEE binary floating point number? • 0 1000 0000 011 0000 0000 0000 0000 0000 • Which of the following floating point numbers is larger? • A = 1 00111111 11110000000000000000000 • B = 1 10001110 00010000000000000000101 Xiaoyu Zhang, CSUSM

Limitations • Overflow: • The number is too big to be represented • Underflow: • The number is too small to be represented • Gradual underflow: • If the number gets smaller, the number of significant digits gets less • 1.234 • 10Emin • 1.234 • 10Emin / 10 = 0.123 • 10Emin • 0.123 • 10Emin / 10 = 0.012 • 10Emin • 0.012 • 10Emin / 10 = 0.001 • 10Emin • 0.001 • 10Emin / 10 = 0.000 • 10Emin Xiaoyu Zhang, CSUSM

Floating Point Complexities • Operations are somewhat more complicated • In addition to overflow we can have “underflow” • Accuracy can be a big problem • IEEE 754 keeps two extra bits, guard and round • four rounding modes • positive divided by zero yields “infinity” • zero divide by zero yields “not a number” • other complexities • Implementing the standard can be tricky • Not using the standard can be even worse • see text for description of 80x86 and Pentium bug! Xiaoyu Zhang, CSUSM

Floating point addition • Alignment • Addition of significands • Normalization of the result • Rounding • Example in decimal system precision 4 digits • What is 9.999 • 101 + 1.610 • 10-1 ? Xiaoyu Zhang, CSUSM

Example • Aligning the two numbers 9.999 • 101 and 1.610 • 10-1 • 9.999 • 101 • 0.01610 • 101 Truncation • 0.016 • 101 • Addition • 9.999 • 101 • + 0.016 • 101 • 10.015 • 101 • Normalization • 1.0015 • 102 • Rounding • 1.002 • 102 Xiaoyu Zhang, CSUSM