Packet Switching Technologies

740 likes | 1.01k Vues

Packet Switching Technologies. Chen- Nien Tsai. Outline. Introduction The Architecture of Switches The Evolution in the Architecture of Switches Switch Architecture Classification Buffering Strategies Output-Buffered Switches Input-Buffered Switches

Packet Switching Technologies

E N D

Presentation Transcript

Packet Switching Technologies Chen-Nien Tsai Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Outline • Introduction • The Architecture of Switches • The Evolution in the Architecture of Switches • Switch Architecture Classification • Buffering Strategies • Output-Buffered Switches • Input-Buffered Switches • Scheduling Algorithms (arbitration schemes) • PIM, iRRM, iSLIP, DRRM Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

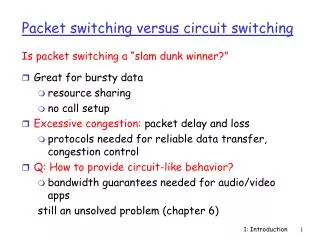

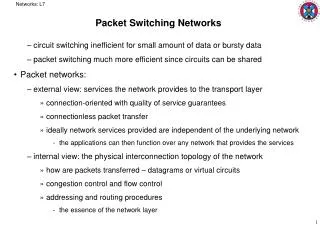

Introduction • A packet switch is a node used to build a network which utilizes the packet switching paradigm for data communication. • ATM switches • IP routers • The high-speed switching technologies are common to both ATM switches and IP routers. • Use a simple term: “switch”. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Fixed vs. Variable Length Data Units • Fixed-length data units are better • Time slots concept • Higher throughput • Simpler hardware design • Variable-length packets are usually segmented into fixed-length data units. • We call these data units “cell” (not necessarily 53 bytes like ATM cells). Time slot Time Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Outline • Introduction • The Architecture of Switches • The Evolution in the Architecture of Switches • Switch Architecture Classification • Buffering Strategies • Output-Buffered Switches • Input-Buffered Switches • Scheduling Algorithms (arbitration schemes) • PIM, iRRM, iSLIP, DRRM Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

The Architecture of Switches Control Functions Datapath Functions Input Ports Output Ports Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Functions of Switches • Datapath Functions • Operations that are performed on every datagram. • Often implemented in special purpose hardware. • Control Functions • Operations that are performed relatively infrequently. • Implemented in software. • System configuration, management, and exchange of routing table information. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

The Evolution in the Architecture of Switches • Bus-based switch with single processor • Bus-based switch with multiple processors • Switch-based switch with multiple processors • Optics Inside a Switch Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Shared Backplane CPU Buffer Memory Routing Table Line Interface CPU Memory Bus-based Switch with Single Processor Typically <0.5Gb/s aggregate capacity Shared Backplane Shared bus Line Interface Line Interface Line Interface MAC MAC MAC Packet arrival • A shared central bus and a central CPU/memory • Bottlenecks • The central CPU must process every packets. • Every packet has to traverse twice through the shared bus

Bus-based Switch with Multiple Processors Fwding Cache Typically < 5Gb/s aggregate capacity • Parallelism can increase the system throughput. • Each packet traverse the bus once. • The central CPU maintain the Routing tables. • The shared bus is still a bottleneck. Cache update CPU Buffer Memory Routing Table Shared bus Line Card Line Card Line Card Buffer Memory Buffer Memory Buffer Memory Fwding Cache Fwding Cache MAC MAC MAC Packet arrival Local process forwarding

Switch-based Switch with Multiple Processors Fwding Engine Typically < 50Gb/s aggregate capacity • Replacing shared bus with a switched fabric. • Multiple packets can be transferred across the fabric simultaneously. Switched Fabric Line Card CPU Card Line Card Local Buffer Memory Local Buffer Memory Routing Table Fwding Engine MAC MAC Local process forwarding Packet arrival Packet arrival Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Why Switched Fabric? • A 16-port IP router, with each port operating at 2.4 Gb/s. • If all of the line cards wish to transfer datagrams simultaneously, requiring a backplane with an aggregate bandwidth of 16 x 2.4 Gb/s = 38.4 Gb/s • It is impractical to build shared backplanes operating at 38.4 Gb/s. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Optics Inside a Switch Optical links 0.72 Tbps OC 768 (39.81 Gbps) Line cards Switch Core 0.3 - 10Tb/s or higher routers in development Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Outline • Introduction • The Architecture of Switches • The Evolution in the Architecture of Switches • Switch Architecture Classification • Buffering Strategies • Output-Buffered Switches • Input-Buffered Switches • Scheduling Algorithms • PIM, iRRM, iSLIP, DRRM Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Switch Architecture Classification • Switches can be classified according to • Switching techniques • Time-Division Switching • Space-Division Switching • Buffering strategies • Input-Buffered Switches • Output-Buffered Switches • Virtual-Output-Queueing Switches Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Switching Techniques Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Time-Division Switching • A single internal communication structure • Shared by all cells traveling from input to output. • Can be a bus, a ring, or a memory. • Advantage • Can easily be extended to support multicast/broadcast operations. • Disadvantage • Capacity limitation of the internal communication structure. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Space-Division Switching • Multiple physical paths are provided • These paths operate concurrently • Multiple cells can be transmitted simultaneously • Advantage • High capacity • Disadvantage • Internal link blocking may occur Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

What is Internal link blocking? Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Space-Division SwitchCrossbar Switches Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Are Crossbar Switches Good? • Advantages • Internally nonblocking • A path is always available to connect an idle input port to an idle output port. • Simple in architecture • Modular • Disadvantage • Need N2crosspoints Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Outline • Introduction • The Architecture of Switches • The Evolution in the Architecture of Switches • Switch Architecture Classification • Buffering Strategies • Output-Buffered Switches • Input-Buffered Switches • Scheduling Algorithms • PIM, iRRM, iSLIP, DRRM Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Why Switches need buffers • Switches need buffers because • Store and forward • Internal link blocking • Output port contention • Buffers are required to be placed somewhere in the switches • to delay packet for not to drop them. Input 1 collision collision Input 2 delayed delayed Output 1 Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

When does Output Port Contention occur? Switch Fabric (nonblocking) Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Classify Switches According to the Buffering Strategies Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

More Buffering Strategies Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Output-Buffered Switches • Most early-date research has focused on this architecture. • Initial demand of switch capacity is low. • A few to 10-20 Gbit/s • 100% throughput • Easier to obtain delay bound. • M/D/1 queue • What if we need more capacity… Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Buffer’s Speed Limits the size of Output-Buffered Switches • Assume • A 24-port ATM switch, with each port operating at 2.4 Gb/s. • The backplane is fast enough • An ATM cell is 53 bytes-long • Transmission time is about 177 ns • Memory access time is 10 ns • If multiple cells are routed to the same output … • Store multiple cells in the output buffer per 177 ns. • The output buffer could not receive all cells. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Input-Buffered Switches • To build larger-scale and higher-speed switches. • Two main problems: • Throughput limitation due to the head-of-line (HOL) blocking. • Only 58.6% throughput can be achieved. • The need of arbitrating cells due to output port contention. • More difficult to obtain delay bound. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

What is HOL Blocking? • Packets destined for other output ports that are free may be blocked. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

A Solution to HOL Blocking: Virtual Output Queueing Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

The Issues of VOQ • An input may have cells granted access by more than one output. • Each input can transfer only one cell a time. • Other cells have to wait, and their corresponding outputs will be idle. Input Output Input Output Input Output 1 1 1 1 1 1 2 2 2 2 2 2 Multiple grants 3 3 3 3 3 3 Idle 4 4 4 4 4 4 Can’t transfer since no grant received Request Grand Transfer Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Scheduling Algorithms • The inefficiency of idle output can be alleviated if the scheduling algorithm runs iteratively. • Parallel Iterative Matching (PIM) • Iterative Round-Robin Matching (iRRM) • Iterative Round-Robin with SLIP (iSLIP) • Dual Round-Robin Matching (DRRM) • They are VOQ-based algorithms and assume nonblocking switch is used (crossbar switch). Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Parallel Iterative Matching (PIM) • Three Steps for each iteration • Request • Each unmatched input sends a request to every output for which it has a queued cell. • Grant • If an unmatched output receives multiple requests, it grants one by randomly selecting a request. • Accept • If an input receives multiple grants, it accepts one by randomly selecting an output. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Why iteration? Input Output Input Output Input Output 1 1 1 1 1 1 2 2 2 2 2 2 Iteration 1 3 3 3 3 3 3 4 4 4 4 4 4 Request Grand Accept Input Output Input Output Input Output 1 1 1 1 1 1 2 2 2 2 2 2 Iteration 2 3 3 3 3 3 3 4 4 4 4 4 4 Request Grand Accept Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

The Problems of PIM • It is difficult and expensive to implement random function at high speed. • PIM could lead to unfairness between connections. • PIM does not perform well for a single iteration. (63% throughput) Flow 1 Flow 2 Flow 3 λ1,1 = 1 2 grants 2 requests μ1,1 = 1/4 Both input 1 and output 1 select flow 1 with 1/2 probability, resulting in the ¼ departure rate. λ1,2 = 1 μ1,2 = 3/4 λ2,1 = 1 μ2,1 = 3/4 Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Iterative Round-Robin Matching (iRRM) • Works similarly to PIM, but uses the round-robin schedulers instead of random selection. • Simple to implement. • Performs fairly. • Two round-robin scheduler (pointers) • Accept pointer aiat input i. • Grant pointer gj at output j. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

iRRM Steps • Request • Each unmatched input sends a request to every output for which it has a queued cell. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

iRRM Steps • Grant • If an unmatched output receives multiple requests, it chooses one that appears next in its round-robin schedule. The pointer gj is incremented to one location beyond the granted input. Output 2 received two requests (Input 1 & 3) Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

iRRM Steps • Accept • If an input receives multiple grants, it accepts one that appears next in its round-robin schedule. The pointer ai is incremented to one location beyond the accepted output. Input 1 received two grants (output 1 & 2) Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

The Problems of iRRM • Does not perform well for a single iteration. 16 x 16 switch Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Iterative Round-Robin with SLIP (iSLIP) • Works similarly to iRRM, but the difference is that the grant pointers update their positions only if their grants are accepted. • 100% throughput with one iteration. • Desynchronization effect. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

iSLIP Steps • Request Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

iSLIP Steps • Grant • If an unmatched output receives multiple requests, it chooses one that appears next in its round-robin schedule. No grant pointers are updated Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

iSLIP Steps • Accept • If an input receives multiple grants, it accepts one that appears next in its round-robin schedule. The pointer aj is incremented to one location beyond the accepted output. The accept pointers are updated only in the first iteration. • Update Grant pointer • The grant pointer gi is is incremented to one location beyond the granted input if and only if the grant is accepted in step 3. The grant pointers are updated only in the first iteration. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

iSLIP Steps Update grant points after the grant is accepted Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

iSLIP achieves 100% throughput • 16 x 16 switches • One iteration Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Desynchronization Effect 1 1 2 2 • Main concept • When a successful matched, output arbiter moves its pointer to one position beyond the granted input, it must be the only output that moves it pointer to that position. 1 1 2 2 1 1 2 2 Both inputs request both outputs. The grant arbiter of output 1 will grant to input 1. 1 1 2 2 In the next time slots, outputs no long contend. 1 1 2 2 1 1 2 2 Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

Dual Round-Robin Matching (DRRM) • Each input arbiter performs request selection. • Sends a request to the output arbiters. Input arbiters update their pointer values. • Each output arbiter performs grant arbitration. Output arbiters update their pointer values. • The output arbiters send grant signals to input arbiters. Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT

DRRM Example Wireless and Broadband Network Laboratory (WBNLAB) Dept. of CSIE, NTUT