Backend Builder

M3T. PU. PU. PU. PU. PU. PU. PU. PU. M. P. M. P. HW Sync. FPU. FPU. . M. P. M. P. M. P. M. Cache. Cache. . M. P. M. Morphable Multithreaded Memory Tiles (M 3 T) Josep Torrellas (University of Illinois at Urbana-Champaign)

Backend Builder

E N D

Presentation Transcript

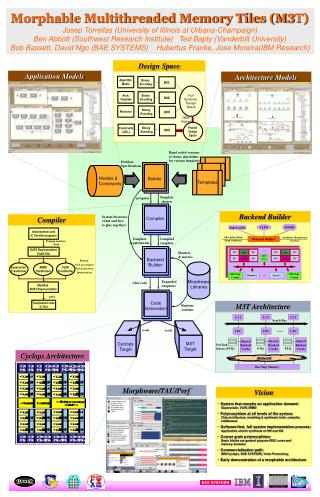

M3T PU PU PU PU PU PU PU PU M P M P HW Sync FPU FPU M P M P M P M Cache Cache M P M Morphable Multithreaded Memory Tiles (M3T) Josep Torrellas (University of Illinois at Urbana-Champaign) Ben Abbott (Southwest Research Institute) Ted Bapty (Vanderbilt University) Bob Bassett, David Ngo (BAE SYSTEMS) Hubertus Franke, Jose Moreira(IBM Research) Design Space Application Models ArchitectureModels Algorithm Model Binary Encoding BDD Full Symbolic Design Space Arch. Template Binary Encoding BDD Resource Binary Encoding BDD OBDD Analysis Pruned Design Space Binary Encoding Constraints (OCL) BDD Hand coded versions of classic algorithms for various templates Problem Specifications Models & Constraints Builder Templates Template chosen pragmas Backend Builder Compiler System Structure (what and how to glue together) Compiler MIMD VLIW Superscalar Instrumented code (C file with pragmas) Allocation Hints from Synthesis Available Morphware Services Backend Builder Template requirements Compiled template Pragma analyzer c2suif SUIF2 Representation (Suif2 file) … Headers & macros Backend Builder Passes: Pick up pragmas Task generation Optimizations Superscalar Transformer MIMD Transformer VLIW Transformer Off-Chip Comm Memory Off-Chip Comm Memory … Morphware Libraries Expanded templates Glue code Modified SUIF2 Representation suif2c Templatized code (C file) Code Generation M3T Architecture Runtime routines L1 I L1 I L1 I Synch Bus CPU CPU CPU a.out a.out Shared Banked Cache Shared Banked Cache Shared Banked Cache M3T Target Cyclops Target PenTask Queue (PTQ) PTQ PTQ Cyclops Architecture Network On-Chip Memory Morphware/TAU/Perf Vision • System that morphs on application demand: Superscalar, VLIW, MIMD • Polymorphism at all levels of the system: Chip architecture, modeling & synthesis tools, compiler, middleware • Software-first, full system implementation process: Application–driven synthesis of HW and SW • Coarse grain polymorphism: Basic blocks are general purpose RISC cores and memory modules • Commercialization path: IBM Cyclops, BAE SYSTEMS, Voice Processing • Early demonstration of a morphable architecture