DIAMOND: Targeting Verification and Reliability Issues in Systems

270 likes | 381 Vues

DIAMOND is an EU FP7 project addressing system verification and reliability challenges. Explore the holistic approach to design and soft errors, with success stories and diagnostics for cosmic radiation and design mistakes. Discover the unified diagnostic model and automated correction techniques for improved system reliability.

DIAMOND: Targeting Verification and Reliability Issues in Systems

E N D

Presentation Transcript

DIAMOND: Targeting Verification and Reliability Issues in Systems Jaan Raik

DIAMOND: Targeting Verification and Reliability Issues in Systems • EU FP7 STREP Project DIAMOND • A holistic view of design and soft errors • Success stories: • FoREnSiC (C, system-level) • zamiaCAD (VHDL/Verilog/SC, RTL) • Follow-up projects • Significance to CEBE

Soft-errors caused by cosmic radiation Design mistakes made by the engineer Soft-errors in new generation chips due to background radiation Electronic systems fail while working in the field DIAMOND’s diagnosis/correction methods The DIAMOND concept

A unified, holistic diagnostic model for bugs and soft errorsat all levels; Automated localisation &correction techniques based on the unified model, both pre-silicon & post-silicon; Implementation of a reasoning framework for localisation &correction, encompassing word-level techniques, formal, semi-formal, and dynamic techniques. DIAMOND: Objectives

DIAMOND Kick-off, Tallinn, February 2-3, 2010 FP7-2009-ICT-4-248613 DIAMOND - Diagnosis, Error Modelling and Correction for Reliable Systems Design Start January 2010; total budget 3.8M € (EU contribution 2.9M €); 462.5 PM The IBM logo is a registered trademark of International Business Machines Corporation (IBM) in the United States and other countries. DIAMOND: FP7 collaborative research

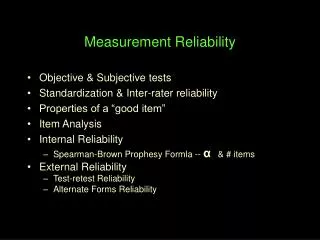

Verification and debug Verification Debug • ~2/3 of development time for verification • ~2/3 of verification time for debug • Thus, nearly half of the development cycle! • Automation of the debug step needed...

Traditional debug flow ??? Spec Design Counter-examples (waveforms), failed assertions, ... Verification Error! • Too little information • Too much information

Automated debug flow Spec Design Corrected design, Repair log, ... Verification Error! Error localization Error correction

FoREnSiC • Formalautomated debug environment for ESL HW in C zamiaCAD • Ahighly scalable framework for design analysis and automated debug at RTL (VHDL-centric) DIAMOND Debug Tools

FoREnSiC • FoREnSiC: Formal Repair Environment for Simple C • For system-level HW • Developed by TU Graz, University of Bremen and TUT • Front-end converting simple C descriptions to flowchart model, different debug back-ends • Open source and available at: http://www.informatik.uni-bremen.de/agra/eng/forensic.php

Available FoREnSiC Back-Ends • FoREnSiC includes 3 complementary back-ends: • Symbolic back-end (TU Graz) • Symbolic+concolic engines and model-based diagnosis for localization; template-based correction. • Cut-based back-end (University of Bremen) • Formallyverifies the equivalence between a C programand an implementation in HDL. • Simulation-based back-end (Tallinn University of Technology, University of Verona) • Intended for correcting larger programs. Statistical localization + mutation-based correction

Statistical analysis • Ranking according to suspiciousness: Suspiciousness score Circuit blocks 16

Günter Bartsch, Stuttgart – founder Rainer Dorsch, Stuttgart – Bosch/IBM Tallinn University of Technology • Anton Tšepurov, PhD student • MaksimJenihhin • ValentinTihhomirov, PhD student • SaifAbrar PhD student • JaanRaik IBM Faculty Award 2011/2012 zamiaCAD team and cooperation

http://zamiacad.sf.net Front-end currently supports VHDL Object database ZDB • Persistence • Scalability • Custom designed • Highly optimized for performance zamiaCAD flow

A case study on ROBSY microprocessor 17k lines of VHDL code Error localization based on statistical ranking zamiaCAD Evaluation

DIAMOND results • Publications • 2 papers at IEEE D&T, 2 papers at JETTA, ... • PhD defenses • 2012, S.Kostin, A.Tšertov, A.Karputkin, T.Viilukas • 2013, I.Aleksejev, A.Tšepurov, U.Reinsalu • Follow-up projects • FP7 STREP BASTION • 3 EU COST Actions • 1 Estonian ICT programme

ICT COST Actions • Rich-model toolkit: an infrastructure for reliable computer systems • 2009 oct. – 2013 oct. • Median: manufacturable and dependable multicore architectures at nanoscale • 2011 dec. – 2015 nov. • Trustworthy Manufacturing and Utilization of Secure Devices (TRUDEVICE) • 2012- 2016

ICTP FUSETEST • Functional Self‐Test, Self‐Diagnosis and Failure Analysis for Integrated Electronics Systems(FUSETEST) • Partner: Testonica • 2013 apr. – 2015 aug.

Significance to CEBE • Verification and correction of bugs in the CEBE processor family • Application of design error correction engines in fine-tuning medical algorithms

Thank you! More info: www.fp7-diamond.eu