JOP Java Optimized Processor

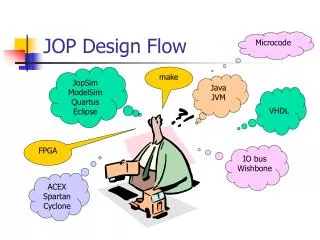

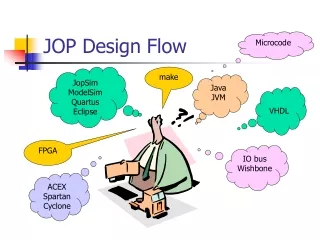

JOP Java Optimized Processor. DI Martin Schöberl. Content. Targets Java Virtal Machine Three different architectures Datapath of JOP3 First results. Targets. Small processor Fits in a main stram FPGA Efficient execution of byte codes JVM real time enabled

JOP Java Optimized Processor

E N D

Presentation Transcript

JOPJava Optimized Processor DI Martin Schöberl

Content • Targets • Java Virtal Machine • Three different architectures • Datapath of JOP3 • First results

Targets • Small processor • Fits in a main stram FPGA • Efficient execution of byte codes • JVM real time enabled • organization of local memory ? • Multi processor on a single chip ?

Java Virtual Machine • 32 (64) Bit stack machine • Variable length instructions • Simple to very complex instructions • Symbolic references • Stack, heap, constants and code

First Approach • Accu/Register Machine • RISC like instruction set • 16 Bit instruction set • 32 Bit datapath • 3 stage pipeline • All instructions single cycle • Larg register file (up to 1024) • JVM complete in SW

Second Approach • + special register SP, AR • 16 register + 16 constants • Stack in local memory • 8 Bit instruction • Memory interface ‚extern‘ • Byte code fetch/decode in HW • 2+3 stage pipeline • JVM instruction min. 3 cycles

JOP3 • Stack machine • Byte code is instruction set • 8 Bit microcode • Basic JVM instructions single cycle • 4 stage pipeline • No traps for complex instructions

JOP3 Fetch P C + 1 RAM jbc J I N S ROM microcode I R + J B R J P C A O P D H + -3 1 +

JOP3 Read/Write A SP vp 1 + 1 SPM vp 2 + + -1 2 SPP A vp 3 + + 1 3 R D A D D R W R A D D R I R SPM vp ix J I N S + vp A cp ix + cp A

JOP3 Execute - + B A RAM wraddr dout wrena rdaddr din ld and or xor shr sp vp0 cp imm I O R

Status • Cores run on Altera ACEX 1K30-3 • Periphery: IO port, SRAM- and Flash interface, UART, ECP • First real application under development

Performance • ‚useless‘ benchmark (prime) • 486SX25: 1.2M transistors e.g. 300k gates • ACEX 1K30: 24 MHz, 30k gates

http://www.jopdesign.com/ • Documentation as HTML • All VHDL, ASM and Java sources • Actual version for download