v8.2 System Generator Audio Quick Start

v8.2 System Generator Audio Quick Start. XUP Virtex-II Pro. Agenda. Requirements Installation Getting Started Explore Use Models Simulink Simulation Hardware-in-the-loop Verification Full Deployment Appendix. Prerequisites. Understanding of the following topics Digital Logic Design

v8.2 System Generator Audio Quick Start

E N D

Presentation Transcript

v8.2 System GeneratorAudio Quick Start XUP Virtex-II Pro

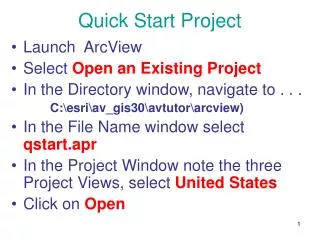

Agenda • Requirements • Installation • Getting Started • Explore Use Models • Simulink Simulation • Hardware-in-the-loop Verification • Full Deployment • Appendix

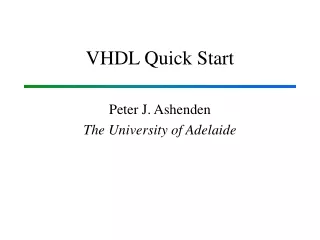

Prerequisites • Understanding of the following topics • Digital Logic Design • Basics of VHDL or Verilog • Digital Signal Processing • Knowledge of the following software • Mathworks Matlab/Simulink Software • ISE Foundation

Required Tools • Mathworks Software • Matlab and Simulink Release R14.3 or R2006a • Signal Processing Blockset • Xilinx software (refer to online donation request form at www.xilinx.com/univ) • v8.2 System Generator for DSP • v8.2 ISE Foundation + latest service pack • V8.2 Chipscope-Pro • Hardware • XUP Virtex-2 Pro Board + Power Supply + USB cable • PC with sound card • Audio PC cable (connect from headphone jack of PC to Line in of XUP board) • Speakers or headphones • Board Support Package Files • Refer to XUPV2PRO_bsp.ppt in /bsp directory

Agenda • Requirements • Installation • Getting Started • Explore Use Models • Simulink Simulation • Hardware-in-the-loop Verification • Full Deployment • Appendix

Installation Procedure • Install ISE Foundation • Install Chipscope-Pro • Install Mathworks Software (Matlab/Simulink + Signal Processing Blockset) • Download System Generator and run the executable to install System Generator for DSP • Install the board support package files in the SysGen install path (see following slides)

System Generator Installation • Double-click on • Executable To install Download to Temporary directory • Run through setup

Board Support Package Installation • Unzip plugins.zip into plugins directory in System Generator install path (ie. C:\MATLAB701\toolbox\xilinx\sysgen\) • This installs BSP files for both JTAG co-simulation and standalone audio • Refer to XUPV2PRO_bsp.ppt for more information Unzip plugins.zip from distribution in System Generator install path

Agenda • Requirements • Software Installation • Getting Started • Explore Use Models • Simulink Simulation • Hardware-in-the-loop Verification • Full Deployment • Appendix

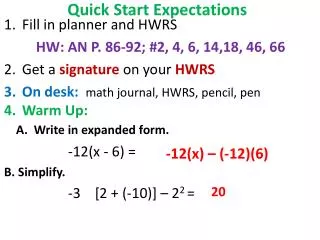

Open Audio Design Browse to \design directory • Double-click on audio.mdl to open Simulink model Refer to Matlab Help for more information

Audio Design Overview audio.mdl (do not change file name) SysGen token controls simulations & Implementations User design (reverb example) 16 KHz Mono wave File input source 16 KHz processed Audio output Don’t change the names on The gateway in/out blocks (see XUPV2PRO_bsp.ppt in /bsp directory)

User Design Reverb Example Select user design In hierarchy Reverb algorithm Consists of adders And delays

Agenda • Requirements • Installation • Getting Started • Three Use Models • Simulink Simulation • Hardware-in-the-loop Verification • Full Deployment • Appendix

Three Use Models • Simulate a System Generator design in Simulink • Hardware-in-the-Loop • Quickly test design in hardware using the JTAG connection on the XUP board • Full Deployment • Standalone design that will operate with Audio CODEC on the XUP board

Agenda • Requirements • Installation • Getting Started • Three Use Models • Simulink Simulation • Hardware-in-the-loop Verification • Full Deployment • Appendix

Simulink Simulation • Simulate the algorithm and verify operation • Simulate design (reverb) in Simulink using yabu_sample_16_mono.wav audio input file • Double-click audio.wav in project directory and listen to processed output on PC speakers

Simulink System Period • Double-Click on the System Generator Token • Set to 41.66 ns (24 MHz) clock rate. • Set to Tsysclk*1500 (16KHz), where Tsysclk is set to 1/24MHz in Matlab workspace. Refer to XUPV2P_bsp.ppt in /bsp directory for more information

Simulate Design • Set the simulation (simulation Configuration Options) start/stop time to capture 80456 audio samples (size of input wave file) • Listen to audio.wav after simulation is complete • Start the simulation

Agenda • Requirements • Installation • Getting Started • Explore Use Models • Simulink Simulation • Hardware-in-the-loop Verification • Full Deployment • Appendix

Hardware-in-the-Loop • Quickly verify algorithm in FPGA by establishing communication between Simulink and target board • Select JTAG co-simulation board support package via the System Generator token • Click “Generate” in System Generator token to create a new JTAG co-simulation Simulink block representing implemented design • System Generator generates HDL from design and adds JTAG interface circuitry • System Generator invokes ISE to create bitstream • System Generator generates a hardware block that represents FPGA hardware model of design • Connect hardware block in design and simulate in Simulink • Bitstream is downloaded to FPGA via JTAG download cable • Simulink transmits sample to FPGA for processing via Simulink sources • FPGA transmits processed signals to Simulink • User can view processed samples using available Simulink sinks

Generate Hardware JTAG Co-Simulation Block • Select XUPV2PRO JTAG co-simulation BSP Double-click SysGen token • Select target directory JTAG co-sim Block generated • Set system rate to 16 KHz • Click Generate button FPGA implementation may take several minutes

Complete Design See audio_hwcosim.mdl for solution • Double-click on HW co-sim block and set download cable to Platform USB • Add and connect HW Co-sim block to the design Wave file called audio_jtagcosim.wav in completed example

Perform JTAG Co-Simulation Board should be Connected and Powered Up • Set the simulation (simulation Configuration Options) start/stop time to capture 8046 audio samples (size of input audio wave file) • Start the simulation • Listen to audio_jtagcosim.wav after simulation is complete

Agenda • Requirements • Installation • Getting Started • Explore Use Models • Simulink Simulation • Hardware-in-the-loop Verification • Full Deployment • Appendix

Full Deployment • Implement an algorithm in hardware that includes the interface to the Audio CODEC on the XUP board • Select the audio board support package via the System Generator token • Enter the correct Simulink System Period to enable a 24MHz clock rate • Specify the target directory • Click generate in token to generate the bitstream that configures the FPGA • System Generator generates HDL from design • System Generator synthesizes HDL to generate .ngc netlist • System Generator merges design NGC with Wrapper NGC during translate phase of implementation • System Generator generates standalone bitstream • User downloads bitstream to FPGA and verifies operation • Connect download cable and power up board • Connect audio cable between PC sound card headphone jack and line-in jack on XUP board • Connect speakers to amp out jack of XUP board • Invoke impact and configure FPGA • Play audio wave file and listen to processed audio output • If operation not successful, use Chipscope-Pro to debug interface

Generate Bitstream Standalone Hardware Select the XUP V2PRO Bitstream SysGen generates HDL and automatically invokes ISE tools to generate bitstream Select target directory FPGA clock must correspond to DCM output frequency in Top-level wrapper ISE status information displayed • Set the simulink system period to 1/24MHz • Click Generate to generate bitstream

Sample Rates Ignore warning message System Generator design data Rate is 16KHz, but clocked at 24MHz in hardware Refer to XUPV2P_bsp.ppt in /bsp directory for more information

Configure FPGA iMPACT Programmer Provided with ISE Foundation • Connect cables (audio, headphones, standard USB cable for configuration, power) • Power up board • Invoke standalone IMPACT programmer and configure FPGA • Start Programs Xilinx ISE 8.2i Accessories iMPACT • Refer to ISE Software Manuals at www.xilinx.com/support • Listen to processed audio generated from XUP Virtex-II Pro board

Chipscope-Pro Useful for verifying on-chip operation • Chipscope-Pro Cores have been inserted in the wrapper • ILA (integrated logic analyzer) cores are connected to the AC97 controller • Captures signals using internal FPGA Block Memory • ICON core connects ILA cores to internal FPGA JTAG circuitry • Trigger conditions and captured signals are communicated via JTAG • Chipscope Analyzer software • Download bitstream via JTAG • Set trigger conditions and view captured results Refer to /chipscope directory for more information

Appendix B Analyzing the Implemented Results

Analyzing the Implemented Design • Useful to review various report files to debug warning and error messages • Design has removed due to load-less nets • Design does not fit into device • Design does not meet timing • Etc. • System Generator must inform ISE software how fast design needs to run • System Generator generates an XCF (XST constraints file) that contains timing information

Warnings and Errors See xflow_results in target directory System Generator .NGC netlist file Contains timing constraints generated from SysGen Top-level wrapper constraints Merged netlist containing wrapper file And SysGen design

Design Size What if design is too big for the target device? Analyze FPGA resource utilization Refer to the map report <design> .mrp generated in the xflow directory Additional information

Design Timing What if my design does not meet timing? Analyze global clock signals Refer to the place & route report <design> .par generated in the xflow directory Analyze global timing results

Timing Analysis How can I view detailed timing information? Start Programs Xilinx ISE Accessories Timing Analyzer Timing Constraint Detailed path information from Source to destination

Constraints Where are the design Constraints? • System Generator generates a pre-synthesis constraints file (XCF) with timing constraints • Period Constraint ( specified by user according to DCM clock output frequency in wrapper) • Multicycle Path Constraints if design has multiple rates • Full deployment BSP includes UCF • Period Constraint for system clock (100 MHz on XUP board) • Pin location constraints • Constraints from both files are merged into PCF (physical constraints file) during implementation Detailed information on timing constraints can be found in the online software manuals www.xilinx.com/support

User Constraints File The BSP contains pin locations and timing constraints for the XUP board System Clock location on XUP board Clock period constraint Pin locations of AC97 CODEC interface signals

XST Constraints File The XCF file contains timing constraints as specified in the System Generator Design FPGA clock period specified in System Generator Token (corresponds to DCM output clock frequency in wrapper file)