LEON-2: General Purpose Processor for a Wireless Engine

Z. Stamenkovi ć. LEON-2: General Purpose Processor for a Wireless Engine. Application. Location Aware Service Platform. picoJava Java VM. Application. Management: Power consumption Performance. Presentation. Session. Transport (TCP). Data Link Control. Network (IP). Physical.

LEON-2: General Purpose Processor for a Wireless Engine

E N D

Presentation Transcript

Z. Stamenković LEON-2: General Purpose Processorfor a Wireless Engine

Application Location Aware Service Platform picoJava Java VM Application • Management: • Power consumption • Performance Presentation Session Transport (TCP) Data Link Control Network (IP) Physical Concept • To realize a vertical strategy from application to silicon

Power Management Test Engine Power Protocol Engine Protocol Application Engine Application Test Engine Engine Management Engine DLC Baseband RF Baseband DLC RF Wireless Engine • Vertical approach from application to silicon can significantly improve the inter-layer performance characteristics • Wireless engine is a system-on-chip solution for mobile computing terminals based on the vertical approach

App TCP IP Management DLC PHY Wireless Engine Projects • Wireless Broadband Network (WBN) • Single chip communication system for wireless data transfer in the 5GHz band with a rate of about 6 to 54 Mbit/s • Wireless Internet (WI) • Vertical protocol optimization: power efficiency, performance • Mobile Computing (MoCo) • Service platform: • Location aware • Java based

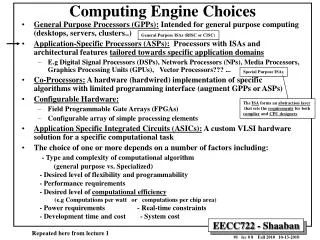

I-Cache DSU DCL CPU AHB Controller AHB Irq Ctrl IO Port D-Cache AHB/APBBridge Memory Controller APB Timers UARTs SRAM Flash LEON-2 Processor System

Implementation of LEON-2 Processor System • Installation of the release • Adaptation of the configuration tool (to include IHP’s library) • Implementation of data and instruction caches • Implementation of BIST logic for SRAMs • Logic synthesis of the design • Implementation of scan chain • Generation of the chip layout • Simulation (functional, post-synthesis and post-layout net-list) • Scan test vectors generation (ATPG) • BIST and scan test simulation • Adaptation of testbenches (SPARC CC installed) • EVCD test vectors generation (with and without timing data) • Test specification • Documentation