Schedule and resources

Schedule and resources. SPIDER has been streamlined to cover: 1) 1 submission ‘small pixel’ ISIS (vertexing/tracking - LCFI ) test chip 2) 1 optimised CMOS pixel detector optimised for vertexing/tracking 3) 1 submission large TPAC ( CALICE ) test chip

Schedule and resources

E N D

Presentation Transcript

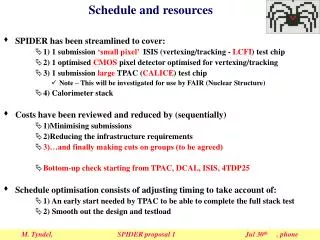

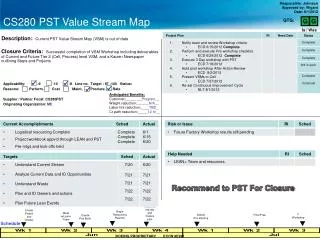

Schedule and resources • SPIDER has been streamlined to cover: • 1) 1 submission ‘small pixel’ ISIS (vertexing/tracking - LCFI) test chip • 2) 1 optimised CMOS pixel detector optimised for vertexing/tracking • 3) 1 submission large TPAC (CALICE) test chip • Note – This will be investigated for use by FAIR (Nuclear Structure) • 4) Calorimeter stack • Costs have been reviewed and reduced by (sequentially) • 1)Minimising submissions • 2)Reducing the infrastructure requirements • 3)…and finally making cuts on groups (to be agreed) • Bottom-up check starting from TPAC, DCAL, ISIS, 4TDP25 • Schedule optimisation consists of adjusting timing to take account of: • 1) An early start needed by TPAC to be able to complete the full stack test • 2) Smooth out the design and testload M. Tyndel, SPIDER proposal 1 Jul 30th , phone

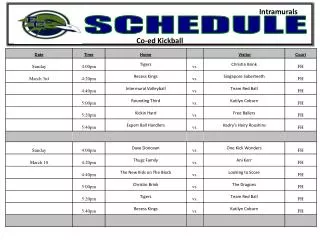

Schedule and resources • Thanks to Renato (he is prepared to support us making an early start) there are 2 options to consider: • 4TDP25 (Jessica) late • Peaked design and test workload • 4TDP25 is on critical path • Exposes 4TDP25 and/or the DCAL stack to risk of being cut • 4TDP25 (Jessica) early • Requires more design effort early in the program • Provides less risk to tracking/vertexing part • Exposes DCAL stack to risk of being cut M. Tyndel, SPIDER proposal 2 Jul 30th , phone

Option-i (4TDP25 late) M. Tyndel, SPIDER proposal 3 Jul 30th , phone

Option-ii (4TDP25 early) M. Tyndel, SPIDER proposal 4 Jul 30th , phone

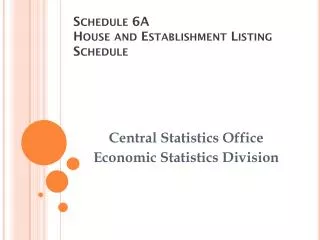

Resource reduction log M. Tyndel, SPIDER proposal 5 Jul 30th , phone

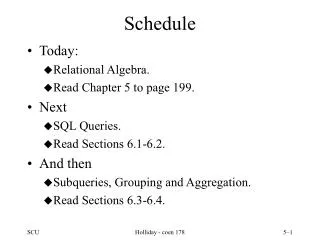

Bottom-up estimate of effort • ISIS (Andrei) • 7fte (including 0.55 TD design) + £295K = £ 810K • Missing Bristol effort, test beam, travel £250K? • T4DP25 • 5.4fte (including 0.5TD design + 0.5 early) + £60K = £ 450K • Missing TD effort testing, travel £ 50K • TPAC + DCAL • 13.8fte (including 1.8TD design) +£ 410K =£1167K • Over-optimistic £200K • Total =£2427 - £2937 M. Tyndel, SPIDER proposal 6 Jul 30th , phone

Bottom-up estimate of effort • Effort evaluation M. Tyndel, SPIDER proposal 7 Jul 30th , phone