Engineering Test Coverage on Complex Sockets

Engineering Test Coverage on Complex Sockets. Myron Schneider. Purpose. Obtain the maximum possible test coverage on a complex socket with a reliable and cost-effective approach. … including fixed pins and inaccessible pins. Outline. The Importance of Socket Test Coverage

Engineering Test Coverage on Complex Sockets

E N D

Presentation Transcript

Engineering Test Coverage on Complex Sockets Myron Schneider

Purpose • Obtain the maximum possible test coverage on a complex socket with a reliable and cost-effective approach. • … including fixed pins and inaccessible pins

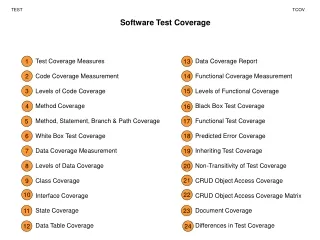

Outline • The Importance of Socket Test Coverage • Pin Classification for the Purposes of Test • Socket Test Methods • Engineered Interposer Design • Results

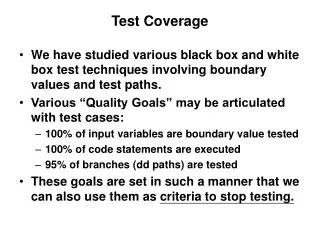

Why is test coverage on sockets important? • Highly integrated target devices • Interconnect matters more • Increased pin density • More emphasis on signal integrity • Grounds are not trivial • Coverage Quality 4

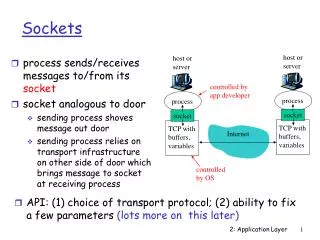

Pin Classification • All pins are not equal for the purposes of test. The effectiveness of some test methods depends on the functionality of the pin tested. • Signal Pins • Fixed Pins Used for Signal Integrity • Fixed Pins Used for Power Distribution • Inaccessible Pins

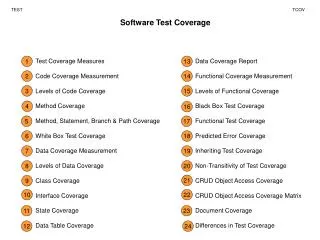

Socket Test Methods • Automated X-Ray Inspection • Functional • Silicon Surrogates • Vector-less test with Network Parameter Measurement (NPM) 8

Engineered Interposer • Utilizes vector-less test since it is an unpowered, cheap, and proven technology • Engineers relationships on a mating PCB to extend NPM technology

Primary Design Constraints • Low Cost • FR4 • Fast turn-around • Standard-cell design and automatic netlist generator • Reliable coverage on maximum number of pins • Engineered redundancy

Interposer Design • Look at CPU datasheet to match all dimensions, pad size and pitch • Find locations of all fixed and inaccessible pins (coverage slightly negotiable) • Run netlist generator software • Layout board • 1.5 days

Diagnostic Software • Needs netlist output to know which relationships are engineered • Accounts for possible variations in interposers, DUTs, insertions, etc. • Aided by statistical methods and engineered redundancy

Results – Seeded Faults • Goal: Validate theory and test out first pass algorithm • 26 seeded defects introduced • Initial algorithm caught all but 3

Results – Production Run • Goal: Use larger sample of boards (that had passed functional test) to investigate algorithm stability and to catch real random defects. • 88 sockets • Found 2 defective pins on 1 socket • No other pins indicted

Conclusion • Effective • Quick to design • Cheap • Low false calls