Advanced FPGA Techniques for Muon Waveform Projection and Shower Background Discrimination

This study presents advanced feature recognition techniques for the IceTop FPGA system, focusing on the projection and reconstruction of muon waveforms onto basis functions. Key highlights include a 2-level trigger system, synchronous waveform capture, and detailed investigations into pedestal variations across different channels. A novel algorithm is introduced for timing and status determination, emphasizing the reduction of dead time using discriminator data. The findings suggest unexpected state dependence in pedestal behavior, with detailed reports and data analysis available for further insights.

Advanced FPGA Techniques for Muon Waveform Projection and Shower Background Discrimination

E N D

Presentation Transcript

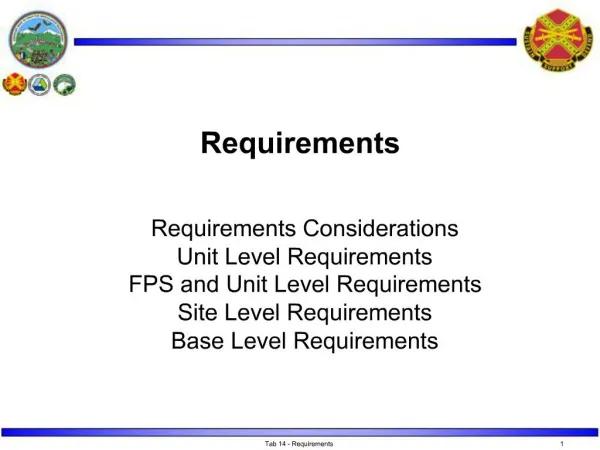

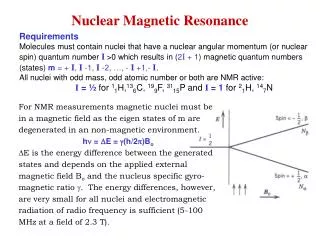

Requirements D. Seckel

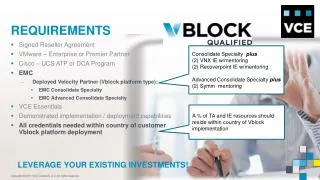

IceTop FPGA Projection of muon waveform onto four basis functions & reconstruction. Rate + Bandwidth m: Advanced feature recognition Þ Shower vs Background e+ e– g: 2-tank coincidence Þ 2-level trigger, fast ATWD decision Rate + Livetime Þ 10 ns + synch. trigger Advanced feature recognition Þ Projection of string-18 SPE waveform w/pedestal & reconstruction. D. Seckel

Studies with String 18 Data • Baseline shifts can be accommodated by method • Synchronous launch can be dealt with • ATWD “fingerprint” • ATWD clocks may differ • State dependence: “An unexpected outcome of this study is that the pedestal for triggered single pe waveforms is different from that for unbiased waveforms.” • Offset of one Clock sample between ATWD 0/1 • Different pedestals in different channels • Reports available at ftp://ftp.bartol.udel.edu/seckel/icetop/misc_eng/string18_rpt_1.pdf ftp://ftp.bartol.udel.edu/seckel/icetop/misc_eng/dom1023-ped-rpt.pdf ftp://ftp.bartol.udel.edu/seckel/icetop/misc_eng/more_atwd_rpt.pdf D. Seckel

FX algorithm (based on string 18) • Determine status (ATWD, co-in, trigger, …) • Capture waveform • Subtract ATWD pedestal • Subtract trigger pedestal • Shift peak (Dt) • Normalize (A = Si wi2 • Project onto (3-4) basis functions • Check quality • Return(t0, Dt, status, ci, A) • 4,1,1,6,2 - 14 bytes D. Seckel

Coincidence timing D. Seckel

ATWD Channel selection • Goal: Reduce dead time • Use both discriminators • If (D1 + !D2) => ATWD-0 • If (D1 + D2) => ATWD-1 • If saturated, acquire ATWD-2 Could do ATWD-2, depending on details D. Seckel

Disc. Start Inc. Counter Ping-Pong Busy Acquire I Acquire II Waveform Buffer FPGA flow IA D1 – AS D2 – x AS Start Acquire Get Time Launch ATWD Launch Coin. Wait for ATWD D2? Read ATWD-1 Read ATWD-0 Saturated? Read ATWD-1 Waveform buffer Stop D. Seckel

Start Acquire Disc. Start Get Time Inc. Counter Launch ATWD Wait for ATWD Ping-Pong > A0 Counter Busy Acquire I Acquire II Set SPE bit Waveform Buffer Launch Coin. Reset Counter Waveform buffer Stop FPGA flow IB D1 – spe D2 – AS D. Seckel

FPGA flow II Get WF Check Coincidence Feature Extraction Send Full Report Priority FX ? Send FX Report > Am Coin + >AS? Send FX Report Coin + >AS? Send Full Report D. Seckel

Calibration • Discriminator • Pedestals • ATWD (A/B, 0/1/2) • Trigger condition (noise) • Basis functions • Impulsive event (m) • Shower (?) • ATWD • Baseline: included in pedestal and basis functions • Abs gain: calibrate to spe at ref HV • Rel gain: common signals in ATWDs D. Seckel

Reconstruction • Apply process • Amplitude from c1 • Time correction from c2, f2= f1’(t) FX D. Seckel