RAM

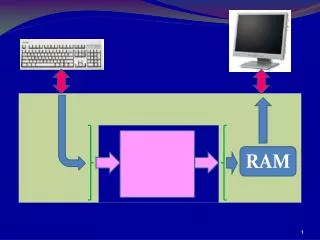

RAM. PS2_Keyboard: entity work.Keyboard generic map (AddressBits => ADDRESSLENGTH) port map ( Reset => Reset, Clock => ClockVGA, PS2Clock => PS2Clock, PS2Data => PS2Data, ASCII => ASCII, WriteEnable => WriteEnable,

RAM

E N D

Presentation Transcript

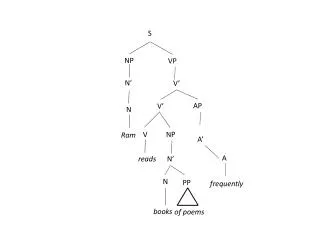

PS2_Keyboard: entity work.Keyboard generic map (AddressBits => ADDRESSLENGTH) port map ( Reset => Reset, Clock => ClockVGA, PS2Clock => PS2Clock, PS2Data => PS2Data, ASCII => ASCII, WriteEnable => WriteEnable, WriteAddress => WriteAddress); ---------- APPLICATION-SPECIFIC BLOCK B e g i n ---------- Input from keyboard and output to VGA RAM Arithmetic: entity work.ArithmeticBlock generic map ( AddressBits => ADDRESSLENGTH, StateMaxValue => 52, NumberOfColumns => TEXTCOLUMNS ) port map ( ASCII_in => ASCII, ASCII_out => RAMData, Address_in => WriteAddress, Address_out => RAMWriteAddress, clk => ClockVGA, rst => Reset, WE_in => WriteEnable, WE_out => RAMWriteEnable); ---------- APPLICATION-SPECIFIC BLOCK E n d ASCII code WriteEnable Arithmetic WriteAddress

ASCII VGA_RAM: entity work.RAM generic map ( AddressBits => ADDRESSLENGTH, DataBits => 8) port map ( Clock => ClockVGA, WriteAddress => RAMWriteAddress, WriteEnable => RAMWriteEnable, DataIn => RAMData, ReadAddress => ReadAddress, DataOut => SymbolPos); WE WA ---------- APPLICATION-SPECIFIC BLOCK B e g i n ---------- Input from keyboard and output to VGA RAM Arithmetic: entity work.ArithmeticBlock generic map ( AddressBits => ADDRESSLENGTH, StateMaxValue => 52, NumberOfColumns => TEXTCOLUMNS ) port map ( ASCII_in => ASCII, ASCII_out => RAMData, Address_in => WriteAddress, Address_out => RAMWriteAddress, clk => ClockVGA, rst => Reset, WE_in => WriteEnable, WE_out => RAMWriteEnable); ---------- APPLICATION-SPECIFIC BLOCK E n d ASCII code WriteEnable Arithmetic WriteAddress

ASCII A WE WA ASCII code RAM WriteEnable Arithmetic WriteAddress Address_out <= conv_std_logic_vector((line*NumberOfColumns + column),AddressBits);

ASCII_out Address_out WE_out ASCII_in Address_in WE_in entity ArithmeticBlock is generic ( AddressBits : natural; StateMaxValue : natural; NumberOfColumns : natural ); Port ( ASCII_in : in STD_LOGIC_VECTOR (7 downto 0); ASCII_out : out STD_LOGIC_VECTOR (7 downto 0); Address_in : in STD_LOGIC_VECTOR (AddressBits - 1 downto 0); Address_out : out STD_LOGIC_VECTOR (AddressBits - 1 downto 0); clk : in STD_LOGIC; rst : in STD_LOGIC; WE_in : in STD_LOGIC; WE_out : out STD_LOGIC ); end ArithmeticBlock; clock (clk) reset (rst) – active ‘1’

architecture Behavioral of ArithmeticBlock is signal Op1 : STD_LOGIC_VECTOR(7 downto 0); -- one decimal digit in binary code signal Op2 : STD_LOGIC_VECTOR(7 downto 0); -- one decimal digit in binary code signal sum : STD_LOGIC_VECTOR(7 downto 0); -- binary signal Difference : STD_LOGIC_VECTOR(7 downto 0); -- binary signal sumMSB : STD_LOGIC_VECTOR(7 downto 0); -- ASCII signal sumLSB : STD_LOGIC_VECTOR(7 downto 0); -- ASCII signal DifLSB : STD_LOGIC_VECTOR(7 downto 0); -- ASCII signal sign : STD_LOGIC_VECTOR(7 downto 0); -- ASCII signal state : integer range 0 to StateMaxValue; signal line, line_local : integer range 0 to 39; signal column, column_local : integer range 0 to 79; signal ASCII_local : std_logic_vector(7 downto 0); signal Operand1: string(1 to 16) := "Operand 1 = "; constant Operand2: string(1 to 16) := "Operand 2 = "; constant SumR: string(1 to 16) := "Sum = "; constant DifR: string(1 to 16) := "Difference = "; sum = Op1 + Op2; Difference = Op1 - Op2;

type rom_type is array (0 to 99) of std_logic_vector (7 downto 0); constant ROM : rom_type := ("00000000","00000001","00000010", "00000011","00000100","00000101","00000110","00000111","00001000", "00001001", "00010000","00010001","00010010", "00010011","00010100","00010101","00010110","00010111","00011000", "00011001", "00100000","00100001","00100010", "00100011","00100100","00100101","00100110","00100111","00101000", "00101001", "00110000","00110001","00110010", "00110011","00110100","00110101","00110110","00110111","00111000", "00111001", "01000000","01000001","01000010", "01000011","01000100","01000101","01000110","01000111","01001000", "01001001", "01010000","01010001","01010010", "01010011","01010100","01010101","01010110","01010111","01011000", "01011001", "01100000","01100001","01100010", "01100011","01100100","01100101","01100110","01100111","01101000", "01101001", "01110000","01110001","01110010", "01110011","01110100","01110101","01110110","01110111","01111000", "01111001", "10000000","10000001","10000010", "10000011","10000100","10000101","10000110","10000111","10001000", "10001001", "10010000","10010001","10010010", "10010011","10010100","10010101","10010110","10010111","10011000", "10011001" );

-- arithmetical operations: sum and difference sum <= ("0000"&(Op1(3 downto 0)))+("0000"&(Op2(3 downto 0))); difference <= ("0000"&(Op1(3 downto 0)))-("0000"&(Op2(3 downto 0))) when ("0000"&(Op1(3 downto 0)))>=("0000"&(Op2(3 downto 0))) else ("0000"&(Op2(3 downto 0)))-("0000"&(Op1(3 downto 0))); sign <= std_logic_vector(to_unsigned(character'pos(' '), 8)) when ("0000"&(Op1(3 downto 0)))>=("0000"&(Op2(3 downto 0))) else std_logic_vector(to_unsigned(character'pos('-'), 8)); sumMSB <= "0011" & ROM(conv_integer(sum))(7 downto 4); sumLSB <= "0011" & ROM(conv_integer(sum))(3 downto 0); DifLSB <= "0011" & ROM(conv_integer(difference))(3 downto 0); -- taking operands from keyboard Op1 <= "00110000" when rst = '1' else ASCII_in when ((ASCII_in >= "00110000") and (ASCII_in <= "00111001")) and (Address_in(0) = '0') and (WE_in = '1'); Op2 <= "00110000" when rst = '1' else ASCII_in when ((ASCII_in >= "00110000") and (ASCII_in <= "00111001")) and (Address_in(0) = '1') and (WE_in = '1');

process(clk, rst) begin if rst = '1' then state <= 0; elsiffalling_edge(clk) then if state=StateMaxValue then state<=0; else state<= state + 1; end if; end if; end process; process(clk, rst) begin if rst= '1' then null; elsifrising_edge(clk) then case state is when 1 to 16 => line_local <= 9; column_local <= 14 + state; ASCII_local <= std_logic_vector(to_unsigned(character'pos(Operand1(state)), 8)); when 17 to 32 => line_local <= 10; column_local <= 14 + state - 16; ASCII_local <= std_logic_vector(to_unsigned(character'pos(Operand2(state-16)), 8)); when 33 => line_local <= 9; column_local <= 14 + 16 + 3; ASCII_local <= Op1; when 34 => line_local <= 10; column_local <= 14 + 16 + 3; ASCII_local <= Op2;

when 1 to 16 => line_local <= 9; column_local <= 14 + state; ASCII_local <= std_logic_vector(to_unsigned(character'pos(Operand1(state)), 8)); signal Operand1: string(1 to 16) := "Operand 1 = "; Operand 1 =

when 33 => line_local <= 9; column_local <= 14 + 16 + 3; ASCII_local <= Op1; Operand 1 =

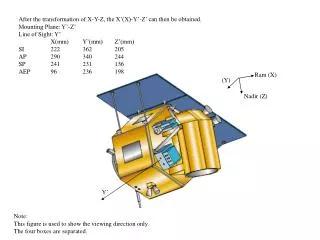

when 35 to 50 => line_local <= 11; column_local <= 14 + state - 34; ASCII_local <= std_logic_vector (to_unsigned(character'pos(SumR(state-34)), 8)); when 51 => line_local <= 11; column_local <= 14 + 16 + 3; ASCII_local <= sumMSB; when 52 => line_local <= 11; column_local <= 14 + 16 + 4; ASCII_local <= sumLSB; when 53 to 68 => line_local <= 12; column_local <= 14 + state - 52; ASCII_local <= std_logic_vector (to_unsigned(character'pos(DifR(state-52)), 8)); when 69 => line_local <= 12; column_local <= 14 + 16 + 3; ASCII_local <= sign; when 70 => line_local <= 12; column_local <= 14 + 16 + 4; ASCII_local <= DifLSB; when others => null; end case; end if; end process;

Op1 = 3 Op2 = 8 Operand 1 = 3 Operand 2 = 8 Sum = 11 Difference = -5