Lecture 14 RTL Design Methodology Part 1: STATISTICS example

Lecture 14 RTL Design Methodology Part 1: STATISTICS example. Structure of a Typical Digital System. Data Inputs. Control Inputs. Control Signals. Datapath ( Execution Unit ). Control ler (Control Unit ). Status Signals. Data Outputs. Control Outputs.

Lecture 14 RTL Design Methodology Part 1: STATISTICS example

E N D

Presentation Transcript

Lecture 14 RTL Design Methodology Part 1: STATISTICS example

Structure of a Typical Digital System Data Inputs Control Inputs Control Signals Datapath (Execution Unit) Controller (Control Unit) Status Signals Data Outputs Control Outputs

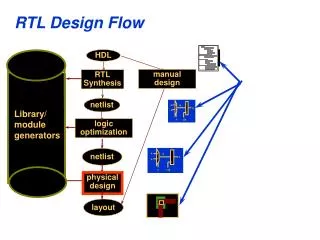

Hardware Design with RTL VHDL Interface Pseudocode Datapath Controller ASM chart Block diagram VHDL code VHDL code

Steps of the Design Process • Text description • Interface • Pseudocode • Block diagram of the Datapath • Interface divided into Datapath and Controller • ASM chart of the Controller • RTL VHDL code of the Datapath, Controller, and Top-Level Unit • Testbench for the Datapath, Controller, and Top-Level Unit • Functional simulation and debugging • Synthesis and post-synthesis simulation • Implementation and timing simulation • Experimental testing using FPGA board

Steps of the Design ProcessIntroduced in Class Today • Text description • Interface • Pseudocode • Block diagram of the Datapath • Interface divided into Datapath and Controller • ASM chart of the Controller • RTL VHDL code of the Datapath, Controller, and Top-level Unit • Testbench for theDatapath, Controller, and Top-Level Unit • Functional simulation and debugging • Synthesis and post-synthesis simulation • Implementation and timing simulation • Experimental testing using FPGA board

Class Exercise 1 STATISTICS

Pseudocode no_1 = no_2 = no_3 = sum = 0 wait for go for i=0 to k-1 do sum = sum + din if din > no_1 then no_3 = no_2 no_2 = no_1 no_1 = din elseif (din > no_2) then no_3 = no_2 no_2 = din elseif (din > no_3) then no_3 = din end if end for avr = sum / k

Circuit Interface clk done reset n n dout Statistics din 2 dout_mode go

STATISTICS: Solutions

din n n n en1 reset en rst n+m clk A gt1 clk n+m no_1 A>B n esum B n reset en rst clk 1 0 s2 clk sum n+m en2 reset enc en reset en rst rst clk clk clk clk A gt2 no_2 m A>B n n+m n B i 1 0 s3 >> m = k-1 en3 reset en rst clk n A gt3 clk A>B avr no_3 zi n B no_3 no_2 no_1 n n n dout_mode 00 01 10 11 2 n dout Block diagram of the Datapath

Interface with the division into the Datapath and Controller din dout_mode clk reset go n 2 gt1 gt2 gt3 Datapath Controller zi en1 en2 en3 esum enc s2 s3 n dout done