Execution Cycle

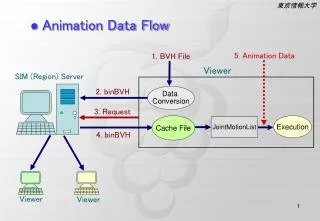

This overview provides a brief yet comprehensive review of the MIPS microarchitecture, focusing on the classic 5-stage execution cycle: Fetch, Decode, Execute, Memory, and Write Back (IF-ID-EX-MEM-WB). It delves into the significance of pipelining, contrasting it against traditional sequential task executions, and highlights the benefits and complexities of RISC versus CISC architectures. The guide also touches on important concepts like endian-ness and potential pipeline hazards, illustrating how efficient instruction execution can be achieved in a CPU.

Execution Cycle

E N D

Presentation Transcript

Outline • (Brief) Review of MIPS Microarchitecture • Execution Cycle • Pipelining • Big vs. Little Endian-ness • CPU Execution Time IF IF IF IF ID ID ID ID EX EX EX EX MEM MEM MEM MEM WB WB WB WB

MIPS Microarchitecture • Recall the datapath for the lw (load word) command

MIPS Microarchitecture • The first step was to fetch the instruction

MIPS Microarchitecture • fetch the instruction

MIPS Microarchitecture • The next step was to decode the instruction

MIPS Microarchitecture • decode the instruction

MIPS Microarchitecture • Next, execute the instruction

MIPS Microarchitecture • execute the instruction

MIPS Microarchitecture • Next, access memory (if necessary)

MIPS Microarchitecture • Finally, write back to a register

MIPS Microarchitecture • write back to a register

MIPS Microarchitecture • Just described classic 5-stage execution cycle • Fetch • Decode • Execute • Memory • Write Back • 5-stage execution cycle typical of RISC machines • RISC is easier to explain • CISC is more complicated… • x86 is CISC

Outline • (Brief) Review of MIPS Microarchitecture • Execution Cycle • Pipelining • Big vs. Little Endian-ness • CPU Execution Time IF IF IF IF ID ID ID ID EX EX EX EX MEM MEM MEM MEM WB WB WB WB

Execution Cycle (aka Instruction Cycle) IF – Instruction Fetch ID – Instruction Decode EX -Execute MEM – Memory WB- Write Back

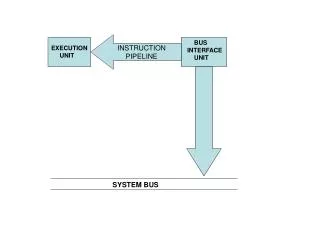

Execution Cycle - Fetch IF • Send the program counter (PC) to memory • fetchthe current instruction from memory • Update the PC • PC = PC + 4 • (since each instruction is four bytes) ID EXE MEM WB

Execution Cycle - Decode IF • Figure out type of instruction (e.g., load, add, etc.) • Based on “opcode” • Determine registers involved • aka “operands” • Get things “setup” for execution • Control Unit sets appropriate pins ID EXE MEM WB

Execution Cycle - Execute IF • ALU operates on operands prepared during decode • ALU performs function based on instruction type • Arithmetic (add, subtract, …) • Logic (equivalence, negation, …) ID EXE MEM WB

Execution Cycle - Memory IF • If instruction is LOAD, • Read data from effective memory address • Effective memory address computed during EXE • If instruction is STORE, • Write data from register to effective memory address • Effective memory address computed during EXE • MEM is an OPTIONAL execution stage • Memory access does not always occur ID EXE MEM WB

Execution Cycle – Write Back IF • Write results “back” to a register • Result type depends on instruction • Results could be from: • ALU computation -or- • Memory access (i.e., load) ID EXE MEM WB

Execution Cycle – Fetch IF • The execution cyclethen repeats… • The next instruction is already indicated by PC • Recall that PC set to PC + 4 during previous fetch ID EXE MEM WB

Outline • (Brief) Review of MIPS Microarchitecture • Execution Cycle • Pipelining • Big vs. Little Endian-ness • CPU Execution Time IF IF IF IF ID ID ID ID EX EX EX EX MEM MEM MEM MEM WB WB WB WB

Pipelining • It’s laundry day, and you have to complete the following tasks: • Wash white clothes in washing machine • Dry white clothes in dryer • Wash color clothes in washing machine • Dry color clothes in dryer • Wash athletic clothes in washing machine • Dry athletic clothes in dryer

Pipelining • Would you do the following? • I.e., Wait for each load to washanddry before starting next? dry colors dry whites wash colors wash whites dry athletic wash athletic time

Pipelining • Heck no!! • What a waste of time!! • What do you do instead? dry colors dry whites wash colors wash whites dry athletic wash athletic time

Pipelining • Overlap: wash one load while another is drying dry whites wash whites wash colors dry colors wash athletic dry athletic time

Pipelining • Do more things at once… dry whites wash whites wash colors dry colors wash athletic dry athletic time

Pipelining • Complete tasks in less time… FREE TIME!!

Pipelining • Can this be applied to the execution cycle? • Yes!! • Fetch the next instruction while decoding the current instruction? • Decode the next instruction while executing the current instruction? • … IF IF ID ID EX EX MEM MEM WB WB

Pipelining • Typical 5-stage pipeline of RISC CPU • 5thinstruction is being fetched while 1stinstruction is being written back • There are much deeper and fancier pipelines… IF IF IF IF IF ID ID ID ID ID EX EX EX EX EX MEM MEM MEM MEM MEM WB WB WB WB WB

Pipelining • Typical 5-stage pipeline of RISC CPU • 9clock cycles to complete5instructions

Pipelining • Without pipelining • 25clock cycles to complete 5instructions … IF IF ID ID EX EX MEM MEM WB WB

Pipelining • There are several things that can disrupt a pipeline • Called hazards • E.g., What happens if the nextinstruction depends on the result of the current instruction?

Pipeline Hazards • Three types of hazards • Control hazard • Data hazard • Structural hazard

Pipeline Hazards: Control • Control Hazard • Occurs when pipelining branches (e.g., if statements) • … or other instructions that change the PC ???

Pipeline Hazards: Data • Data Hazard • Occurs when an instruction tries to use data before it’s available • For example: 1: R1 <- R2 + R3 2: R4 <- R1 + R5 • Contents in R1 (register 1) may have been loaded for instruction#2 beforeinstruction#1 has finished. • Several types of data hazards…

Pipeline Hazards: Data • Data Hazard 1: R1 <- R2 + R3 2: R4 <- R1 + R5 1: 2: IF IF ID ID EX EX MEM MEM WB WB R1 used in instruction #2’s executionbefore instruction #1 writes back

Pipeline Hazards: Structural • Structural Hazard • Occurs when one hardware component is needed by two (pipelined) tasks at same time • Example: read from andwrite to memory at the same time • Fetch an instruction from memory while writing data to memory • Hence why instruction and data memory are separated

Pipelining: Solutions • Ways to minimize pipeline hazards • Stall • Flush • Out-of-order execution • Forwarding • Bypassing • Branch prediction • … • Beyond the scope of this course… • Learn about / master pipeline hazards

Break Time!!! I don’t fish, but this likes nice…

Outline • (Brief) Review of MIPS Microarchitecture • Execution Cycle • Pipelining • Big vs. Little Endian-ness • CPU Execution Time IF IF IF IF ID ID ID ID EX EX EX EX MEM MEM MEM MEM WB WB WB WB

Big vs. Little Endian • Some important jargon: 0x97 46 AB 07 1001 0111 0100 0110 1010 1011 0000 0111 MSB: Most Significant Bit LSB: Least Significant Bit

Big vs. Little Endian 0x97 46 AB 07 1001 0111 0100 0110 1010 1011 0000 0111 Most Significant Byte Least Significant Byte MSB can stand for most significant bit OR byte LSB can stand for least significant bit OR byte

Big vs. Little Endian • Endian refers to the ordering of bytes for multiple byte words • How the bytes are stored in memory • How the bytes are interpreted • Whether the MSB comes “first” or “last” • Whether the LSB comes “first” or “last” MSB - Most Significant Byte LSB - Least Significant Byte

Big Endian • Most significant byte stored at smallestaddress • Least significant bytestored at largest address 0x97 46 AB 07

Little Endian • Most significant byte stored at largest address • Least significant bytestored at smallest address 0x97 46 AB 07

Example • Store 0x46 A0 B7 FF using: Big Endian Little Endian

Example • Store 0x46 A0 B7 FFusing: Big Endian Little Endian

Outline • (Brief) Review of MIPS Microarchitecture • Execution Cycle • Pipelining • Big vs. Little Endian-ness • CPU Execution Time IF IF IF IF ID ID ID ID EX EX EX EX MEM MEM MEM MEM WB WB WB WB