Execution Cycle

This guide explores the execution cycle of Tomasulo's algorithm, emphasizing dynamic data flow and out-of-order execution. It illustrates how various floating-point instructions—such as multiplication, addition, and division—are handled within the CPU. Through detailed cycles, it demonstrates the process of instruction issue, execution, and completion, highlighting register renaming and the management of outstanding loads. The example cycles clarify how dependencies are resolved while maintaining efficient instruction throughput.

Execution Cycle

E N D

Presentation Transcript

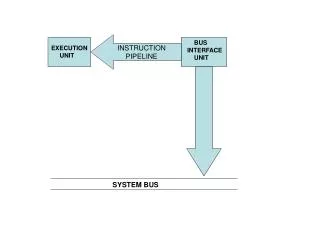

Execution Cycle • Dynamic DLX (much simpler) • 2 FP multiply (10 EX cycles) • 1 FP add (2 EX cycles) • 1 FP divide (40 EX cycles) • 1 integer unit (1 EX cycle)

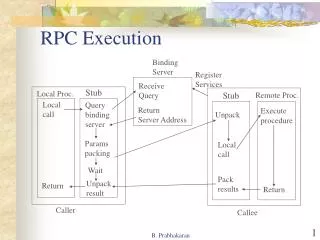

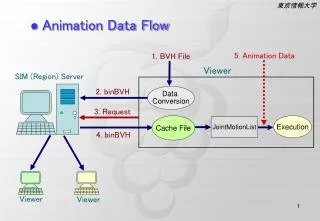

Instruction stream 3 Load/Buffers FU count down 3 FP Adder R.S. 2 FP Mult R.S. Clock cycle counter Tomasulo Example

Tomasulo Example Cycle 2 Note: Can have multiple loads outstanding

Tomasulo Example Cycle 3 • Note: registers names are removed (“renamed”) in Reservation Stations; MULT issued • Load1 completing; what is waiting for Load1?

Tomasulo Example Cycle 4 • Load2 completing; what is waiting for Load2?

Tomasulo Example Cycle 5 • Timer starts down for Add1, Mult1

Tomasulo Example Cycle 6 • Issue ADDD here despite name dependency on F6?

Tomasulo Example Cycle 7 • Add1 (SUBD) completing; what is waiting for it?

Tomasulo Example Cycle 10 • Add2 (ADDD) completing; what is waiting for it?

Tomasulo Example Cycle 11 • Write result of ADDD here? • All quick instructions complete in this cycle!

Tomasulo Example Cycle 15 • Mult1 (MULTD) completing; what is waiting for it?

Tomasulo Example Cycle 16 • Just waiting for Mult2 (DIVD) to complete

Tomasulo Example Cycle 56 • Mult2 (DIVD) is completing; what is waiting for it?

Tomasulo Example Cycle 57 • Once again: In-order issue, out-of-order execution and out-of-order completion.