Dynamic Memory Allocation

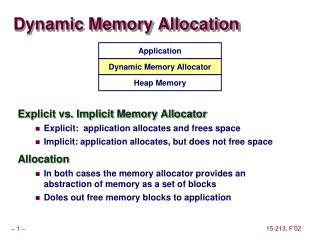

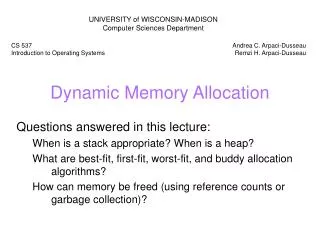

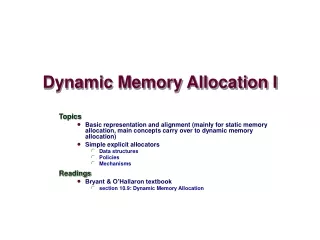

Dynamic Memory Allocation. Outline. Explicit Free List Segregated Free List Suggested reading: 9.9. Explicit free lists. Explicit list among the free blocks using pointers within the free blocks Use data space for link pointers Typically doubly linked

Dynamic Memory Allocation

E N D

Presentation Transcript

Outline • Explicit Free List • Segregated Free List • Suggested reading: 9.9

Explicit free lists • Explicit list among the free blocks using pointers within the free blocks • Use data space for link pointers • Typically doubly linked • Still need boundary tags for coalescing • It is important to realize that links are not necessarily in the same order as the blocks

A B C Forward links A B 4 4 4 4 6 6 4 4 4 4 C Back links Explicit free lists

Freeing with explicit free lists • Where to put the newly freed block in the free list • LIFO (last-in-first-out) policy • insert freed block at the beginning of the free list • pro: simple and constant time • con: studies suggest fragmentation is worse than address ordered.

Freeing with explicit free lists • Where to put the newly freed block in the free list • Address-ordered policy • insert freed blocks so that free list blocks are always in address order • i.e. addr(pred) < addr(curr) < addr(succ) • con: requires search • pro: studies suggest fragmentation is better than LIFO

Segregated Storage • Each size “class” has its own collection of blocks • Often have separate collection for every small size (2,3,4,…) • For larger sizes typically have a collection for each power of 2

1-2 3 4 5-8 9-16 Segregated Storage

Simple segregated storage • Separate heap and free list for each size class • No splitting • To allocate a block of size n: • if free list for size n is not empty, • allocate first block on list (note, list can be implicit or explicit) • if free list is empty, • get a new page • create new free list from all blocks in page • allocate first block on list • constant time

Simple segregated storage • To free a block: • Add to free list • Tradeoffs: • fast, but can fragment badly

Segregated fits • Array of free lists, each one for some size class

Segregated fits • To allocate a block of size n: • search appropriate free list for block of size m > n • if an appropriate block is found: • split block and place fragment on appropriate list (optional) • if no block is found, try next larger class • repeat until block is found • if no blocks is found in all classes, try more heap memory

Segregated fits • To free a block: • coalesce and place on appropriate list (optional) • Tradeoffs • faster search than sequential fits (i.e., log time for power of two size classes) • controls fragmentation • A simple first-fit approximates a best-fit over entire heap • coalescing can increase search times • deferred coalescing can help

Buddy Systems • A special case of segregated fits • Each size is power of 2 • Initialize • A heap of size 2m

Buddy Systems • Allocate • Roundup to power of 2 such as 2k • Find a free block of size 2j (k j m) • Split the block in half until j=k • Each remaining half block (buddy) is placed on the appreciate free list • Free • Continue coalescing with the free buddies

Outline • Random-Access Memory (RAM) • Nonvolatile Memory • Suggested Reading: 6.1

Random-Access Memory (RAM) • Key features • RAM is packaged as a chip. • Basic storage unit is a cell (one bit per cell). • Multiple RAM chips form a memory.

Random-Access Memory (RAM) • Static RAM (SRAM) • Each cell stores bit with a six-transistor circuit. • Retains value indefinitely, as long as it is kept powered. • Relatively insensitive to disturbances such as electrical noise. • Faster and more expensive than DRAM.

Random-Access Memory (RAM) • Dynamic RAM (DRAM) • Each cell stores bit with a capacitor and transistor. • Value must be refreshed every 10-100 ms. • Sensitive to disturbances. • Slower and cheaper than SRAM.

Tran. Access per bit time Persist? Sensitive? Cost Applications SRAM 6 1X Yes No 100x cache memories DRAM 1 10X No Yes 1X Main memories, frame buffers SRAM vs DRAM summary

16 x 8 DRAM chip cols 0 1 2 3 memory controller 2 bits / 0 addr 1 rows supercell (2,1) 2 (to CPU) 3 8 bits / data internal row buffer Conventional DRAM organization • d x w DRAM: • dw total bits organized as d supercells of size w bits pins

16 x 8 DRAM chip cols 0 memory controller 1 2 3 RAS=2 0 2 / addr 1 rows 2 3 8 / data row 2 internal row buffer Reading DRAM supercell (2,1) • Step 1(a): Row access strobe (RAS) selects row 2. • Step 1(b): Row 2 copied from DRAM array to row buffer.

16 x 8 DRAM chip cols 0 memory controller 1 2 3 CAS=1 0 2 / addr 1 rows supercell (2,1) 2 3 8 / data internal row buffer Reading DRAM supercell (2,1) • Step 2(a): Column access strobe (CAS) selects column 1. • Step 2(b): Supercell (2,1) copied from buffer to data lines, and eventually back to the CPU.

addr (row = i, col = j) : supercell (i,j) DRAM 0 64 MB memory module consisting of eight 8Mx8 DRAMs DRAM 7 data bits 56-63 bits 48-55 bits 40-47 bits 32-39 bits 24-31 bits 16-23 bits 8-15 bits 0-7 63 56 55 48 47 40 39 32 31 24 23 16 15 8 7 0 Memory controller 64-bit doubleword at main memory address A 64-bit doubleword to CPU chip Memory modules

Enhanced DRAMs • All enhanced DRAMs are built around the conventional DRAM core • Fast page mode DRAM (FPM DRAM) • Access contents of row with [RAS, CAS, CAS, CAS, CAS] instead of [(RAS,CAS), (RAS,CAS), (RAS,CAS), (RAS,CAS)].

Enhanced DRAMs • Extended data out DRAM (EDO DRAM) • Enhanced FPM DRAM with more closely spaced CAS signals. • Synchronous DRAM (SDRAM) • Driven with rising clock edge instead of asynchronous control signals

Enhanced DRAMs • Double data-rate synchronous DRAM (DDR SDRAM) • Enhancement of SDRAM that uses both clock edges as control signals. • Different sizes of small prefetch buffers that increase the effective bandwidth • DDR (2 bits), DDR2 (4 bits), and DDR3 (8 bits)

Enhanced DRAMs • Rambus DRAM(RDRAM) • An alternative proprietary technology with a higher maximum bandwidth than DDR SDRAM • Video RAM (VRAM) • Like FPM DRAM, but output is produced by shifting row buffer • Dual ported (allows concurrent reads and writes)

Nonvolatile memories • DRAM and SRAM are volatile memories • Lose information if powered off. • Nonvolatile memories retain value even if powered off • Generic name is read-only memory (ROM). • Misleading because some ROMs can be read and modified.

Types of ROMs • Programmable ROM (PROM) • Write once • Erasable programmable ROM (EPROM) • Erase by ultraviolet light • Write by a special device • About 1000 times • Electrically erasable PROM (EEPROM) • Reprogramming in-place on printed circuit cards • Flash memory • Based on EEPROM

Nonvolatile memories • Firmware • Program stored in a ROM • BIOS (basic input/output system) • Boot time code • a small set of primitive input and output functions • graphics cards, disk controllers • Translate I/O (input/output) requests from the CPU