Understanding Unconditional and Conditional Branch Instructions in AVR Assembly

This document outlines the concepts and use of unconditional and conditional branch instructions in AVR assembly language, focusing on the RJMP and JMP instructions. RJMP allows for relative jumps within a 12-bit signed range, while JMP offers absolute jumps within a 22-bit unsigned address range. Additionally, it discusses the status register (SREG), which reflects the status of the last ALU operation, including flags like Zero, Carry, Negative, and Overflow, and how these bits influence conditional branching. Examples demonstrate their application in code.

Understanding Unconditional and Conditional Branch Instructions in AVR Assembly

E N D

Presentation Transcript

Status Register And conditional branching CS-280 Dr. Mark L. Hornick

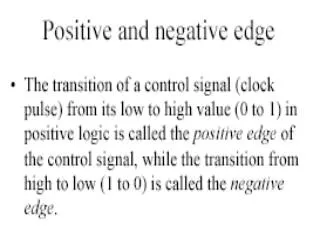

RJMP is an Unconditional Branch instruction • RJMP <addr> • <addr> must be gt -2048 and lt 2047 • i.e. RJMP can branch to addresses relative to the current instruction • 12 bits (bits 0-11) are used for the address • These bits represent a signed value • So bit 11 (s) represents the sign bit 1100 sbbb bbbb bbbb CS-280 Dr. Mark L. Hornick

JMP is another Unconditional Branch instruction • JMP <addr> • <addr> is an absolute program address • i.e. JMP can branch to any absolute address between 0 and 4M • JMP is a 32-bit (2-word) instruction • 22 bits are used for the address • These bits represent an unsigned value 1001 010b bbbb 110b bbbb bbbb bbbb bbbb CS-280 Dr. Mark L. Hornick

SREG is a special-purpose register that indicates the status of the last instruction executed by the ALU These bits are altered automatically by the ALU with each instruction executed.But you can set or clear them explicitly (e.g. use SEH, CLH to set/clear the H flag) CS-280 Dr. Mark L. Hornick

Example: if a register is decremented and the result is 0, the Zero bit (Z) is set by the ALU LDI R20, 1 ;initialize R20 to 1 DEC R20 ;decrement by 1 Z is set if the result of last operation is 0 (if all bits are 0) CS-280 Dr. Mark L. Hornick

Example: if two registers are added together and the unsigned result > 255, the Carry bit (C) is set by the ALU • C is set to 1 if: • addition generates a carry • subtraction produces a borrow • shift or rotate shifts out a 1 LDI R20, 0x80 ; 1000 0000 LDI R21, 0x80 ; 1000 0000 ADD R20, R21 ;1 0000 0000 CS-280 Dr. Mark L. Hornick

Example: if two registers are added together and bit 7 in the result is set to 1, the Negative bit (N) is set by the ALU N is set whenever bit 7 is 1 LDI R20, 0x80 ; 0100 0011 LDI R21, 0x80 ; 0100 0101 ADD R20, R21 ; 1000 1000 CS-280 Dr. Mark L. Hornick

Example: if two registers containing signed values are added together and bit 7 in the result changes, the two’s-complement overflow bit (V) is set by the ALU • V is set to1 if: • positive + positive = negative • negative + negative = positive • Example: 60 + 70 = 130 (>127) LDI R20, 0x80 ; 0011 1100 LDI R21, 0x80 ; 0100 0110 ADD R20, R21 ; 1000 0010 CS-280 Dr. Mark L. Hornick

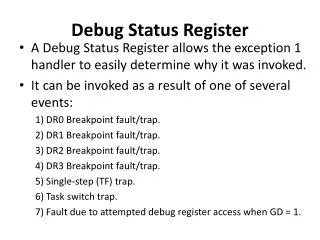

The status of the bits in SREG are used in Conditional Branch instructions • Demo CS-280 Dr. Mark L. Hornick

Conditional Branch instructions that execute according to the settings of the SREG bits Taken from AVR_Instruction_Set.pdf CS-280 Dr. Mark L. Hornick