Satellite Computer System based on LEON Technology

Satellite Computer System based on LEON Technology. Characterization Presentation Spring 2007 – yearly project By Yossi Zadik & Ira Joffe supervised by: Ina Rivkin . Goals. Learning the LEON processor structure : IP cores, IF protocols and usage

Satellite Computer System based on LEON Technology

E N D

Presentation Transcript

Satellite Computer System based on LEON Technology Characterization Presentation Spring 2007 – yearly project By Yossi Zadik & Ira Joffe supervised by: Ina Rivkin

Goals • Learning the LEON processor structure : IP cores, IF protocols and usage • Learning and using in GR tools – compiler, monitor and Simulator • Make System On Chip with the LEON platform • The system will include AMBA bus and IP cores from the GRLIB, and IP core of our own(part B) • Create a simulation and produce a test for the system • Sensitize the system • FPGA implementation

Introduction • The LEON system is based on technology developed by the Gaisler Research Inc. • developed for: critical space systems cost-efficient consumer products. • Requirements: high guarantee for quality cost-sensitive efficiency and low-overhead implementations

Introduction • GRLIB IP Library - a set of IP cores, designed for system-on-chip (SOC) development • AMBA bus - The IP cores are centered around the on-chip bus (AMBA) and connected through it • GRLIB support different CAD tools and target technologies. A plug&play method is used to configure and connect the IP cores • Support products are available in the software level: compiler, monitor and simulator.

LEON 3 – features: • 7 stage pipeline with Harvard architecture • Separate instruction and data caches • Hardware multiplier and divider • On chip debug support • Multi processor extensions

LEON 3 processor core block diagram Integer unit: • Implements full SPARC V8 standard including hardware multiply and divide instructions. • Configurable number of register windows. • Pipeline consists of 7 stages.

LEON 3 processor core block diagram Cache sub-system: • Separate instruction and data cache. Floating-point units and co-processor: • Provides interfaces for a FPU and a custom co-processor. • FPU controller for high performance GRFPU – available from GR. • Execute in parallel with the integer unit

LEON 3 processor core block diagram Memory management unit: • Can be optionally enabled • Implements full SPARC V8 MMU specification, and provides mapping between multiple 32- bit virtual address spaces and 36-bit physical memory. • Can be configured up to 64 fully associative TLB entries

LEON 3 processor core block diagram On-chip debug support: • Allow non intrusive debugging on target hardware. • Up to 4 watch point registers can be enabled. Can be used to enter debug mode when an optional debug support unit is attached. • Interface provides full access to all processor registers and cache.

LEON 3 processor core block diagram Interrupt interface: • Supports SPARC V8 interrupt model with 15 asynchronous interrupts. AMBA interface: • Interface is complaint with AMBA 2.0 standard. • Cache system implements an AMBA AHB master to load/store data from/to the caches.

LEON3FT • The LEON3FT processor is a derivate of the standard LEON3 processor, functionally identical to it, enhanced with fault-tolerance against SEU errors. It is focused on the protection of on-chip RAM blocks, which are used to implement IU/FPU register files and the cache memory.

AMBA BUS • AMABA BUS is a technology independent on-chip protocol. • Defines an on-chip communication standard for designing high performance embedded microcontrollers.

AMBA BUS • 3 types of buses:

Processors and support functions: • LEON3 SPARC V8 32-bit processor • DSU3 Multi-processor Debug support unit • IRQMP Multi-processor Interrupt controller • GRFPU High-performance Floating-point unit • GRFPU-Lite Low-area Floating-point unit • LEON3FT Fault-tolerant SPARC V8 Processor

Floating-point units • GRFPU High-performance IEEE-754 Floating-point unit • GRFPU-Lite Low-area IEEE-754 Floating-point unit MIL-STD-1553 Bus interface • B1553BC 1553 Bus controller with AHB interface • B1553RT 1553 Remote terminal with AHB interface • B1553BRM 1553 BC/RT/Monitor with AHB interface Encryption • GRAES 128-bit AES Encryption/Decryption Core • GRECC Elliptic Curve Cryptography Core

Memory controllers • SRCTRL - PROM/SRAM controller • SDCTRL - SDRAM controller • FTSDCTRL - PC133 SDRAM Controller with EDAC • FTSRCTRL - Fault Tolerant PROM/SRAM/IO Controller • MCTRL - PROM/SRAM/SDRAM controller • FTMCTRL - PROM/SRAM/SDRAM controller with EDAC • AHBSTAT - AHB failing address register • DDRCTRL - DDR controller with two AHB ports (Xilinx only) • DDRSPA - Single-port DDR266 controller (Xilinx and Altera) • SSRCTRL - synchronous SRAM (SSRAM) controller • FTSRCTRL8 - IO Memory Controller with EDAC

AMBA Bus control • AHB2AHB - Uni-directional AHB/AHB Bridge • AHBBRIDGE - Bi-directional AHB/AHB Bridge • AHBCTRL - AMBA AHB bus controller with plug&play • AHBCTRL_MB - AMBA AHB bus controller for multiple buses with plug&play • APBCTRL - AMBA APB Bridge with plug&play • AHBTRACE - AMBA AHB Trace buffer

PCI interface • PCITARGET - target-only PCI interface • PCIMTF/GRPCI - PCI master/target interface with FIFO • PCITRACE - PCI trace buffer • PCIDMA - DMA controller for PCIMTF • PCIARB - PCI Bus arbiter CCSDS Telecommand and telemetry functions • GRTM CCSDS Telemetry encoder • GRTC CCSDS Telecommand decoder • GRPW Packetwire receiver with AHB interface • GRCTM CCSDS Time manager

On-chip memory functions • AHBRAM - Single-port RAM with AHB interface • AHBROM - ROM generator with AHB interface • SYNCRAM - Parametrizable 1-port RAM • SYNCRAM_2P - Parametrizable 2-port RAM • SYNCRAM_DP - Parametrizable dual-port RAM • REGFILE_3P - Parametrizable 3-port register file • FTAHBRAM - RAM with AHB interface and EDAC protection

Serial communication • AHBUART - Serial/AHB debug interface • AHBJTAG - JTAG/AHB debug interface • APBPS2 - PS2 Keyboard interface with APB interface • APBUART - Programmable UART with APB interface • CAN_OC - Opencores CAN 2.0 MAC with AHB interface • GRETH - Gaisler Research 10/100 Ethernet MAC with AHB I/F • GRETH_GIGA - Gaisler Research 10/100/1000 Ethernet MAC with AHB • GRSPW - SpaceWire link with RMAP and AHB interface • USBDCL - USB-2.0 / AHB debug communication link • GRCAN - CAN 2.0 Controller with DMA

Misc. peripherals • ATACTRL - IDE/ATA controller with AHB interface • GPTIMER - Modular timer unit • GPIO - General purpose I/O port • LOGAN - On-chip logic analyzer • TAP - Generic TAP controller • NUHOSP3 - PROM & I/O interface for Nuhorizons Spartan3 board • APBVGA - Text-only VGA controller • CLKGEN - Clock generator and frequency divider for Altera/Xilinx • RSTGEN - Generic reset generator • SVGACTRL - SVGA video frame buffer

Simulation and debugging • SRAM - SRAM simulation model with srecord pre-load • MT48LC16M16 - Micron SDRAM model with srecord pre-load • MT46V16M16 - Micron DDR model • CY7C1354B - Cypress ZBT SSRAM model with srecord pre-load • AHBMSTEM - AHB master simulation model with scripting • AHBSLVEM - AHB slave simulation model with scripting • AMBAMON - AHB and APB protocol monitor

LEON Tools *GRMON and TSIM have evaluation versions (grmon for 21 days), the full versions and GrmonRCP requires payment

GRMON - monitor GRMON is a general debug monitor for the LEON processor,and for SOC designs based on the GRLIB IP library.GRMON includes the following functions: •Read/write access to all system registers and memory •Built-in disassembler and trace buffer management •Downloading and execution of LEON applications •Breakpoint and watchpoint management •Remote connection to GNU debugger (gdb) •Support for USB,JTAG,RS232,PCI,ethernet and spacewire debug links

Platforms supported:Linux-x86,Solaris-2.x,Windows (2K/XP)and Windows with cygwin. After 21 days GRMON needs a license The following features are not available in the evaluation version: •Support for LEON-FT •Loadable modules •Custom LEON2 configuration files •Error injection

GrmonRCP GrmonRCP is a GUI for grmon,based on the Eclipse Rich-Client Protocol. It provides a graphical interface to all Grmon functions. GrmonRCP is available as a separate package

TSIM2 Simulator TSIM is a generic SPARC architecture simulator capable of emulating ERC32- and LEON-based computer systems. TSIM supports the following platforms: solaris-2.8, linux, linux-x64, Windows 2K/XP, and Windows 2K/XP with Cygwin unix emulation.

TSIM provides several unique features(1\2): •Accurate and cycle-true emulation of ERC32 and LEON2/3 processors •Superior performance: +30 MIPS on high-end PC (AMD64@2.4 GHz) •Accelerated simulation during processor standby mode •Standalone operation or remote connection to GNU debugger (gdb) •64-bit time for unlimited simulation periods •Instruction trace buffer •EDAC emulation (ERC32) •MMU emulation (LEON2/3)

More TSIM features(2\2): SDRAM emulation (LEON2/3) •Local scratch-pad RAM (LEON3) •Loadable modules to include user-defined I/O devices •Non-intrusive execution time profiling •Code coverage monitoring •Dual-processor synchronisation •Stack backtrace with symbolic information •Check-pointing capability to save and restore complete simulator state •Also provided as library to be included in larger simulator frameworks

BCC –Bare C Cross Compiler BCC is a cross-compiler for LEON2 and LEON3 processors.It is based one the GNU compiler tools and the Newlib standalone C-library. The cross-compiler system allows compilation of both tasking and non-tasking C and C++ applications. It supports hard and soft floating point operations, as well as SPARC V8 multiply and divide instructions. BCC can also be used to compile the eCos kernel.

BCC consists of the following packages: •GNU GCC C/C++compiler v3.4.4 •Newlib C-library v 1.13.1 •Low-level I/O routines for LEON2 and LEON3,including interrupt support •uIP light-weight TCP/IP stack •GDB debugger v6.4 with DDD and Insight Graphical front-end •Mkprom prom-builder for LEON2/3 •Linux and Windows/Cygwin hosts

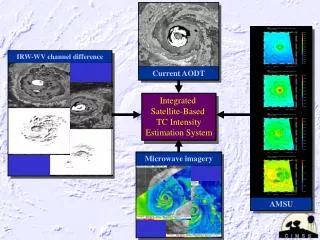

The Project Roadmap First semester: • Building the system as illustrated • System simulation • Synthesis Secondsemester: • User core • Spacewire core • FPGA implementation

Time table to mid semester presentation • WW19: characterization presentation • WW20: get to know GRLIB and all IP cores • WW21: decide which IP cores we will use for our first semester system, and check availability. • WW22: tools selection based on experimenting • WW23: make mid semester presentation.