SRAM design for VFAT3

SRAM design for VFAT3. CERN – Round Table Meeting - July 4 th Jérôme Masson. Outline. Work done since May 22th (CERN workshop) Modifications to bring What I need to do before end of July. Reminder : Block diagram. DataIN SRAM1 128. DataIN SRAM2 128. Encoder. Decoder. Encoder.

SRAM design for VFAT3

E N D

Presentation Transcript

SRAM design for VFAT3 CERN – Round Table Meeting - July 4th Jérôme Masson

Outline • Work done since May 22th (CERN workshop) • Modifications to bring • What I need to do before end of July Round Table Meeting

Reminder : Block diagram DataIN SRAM1128 DataIN SRAM2128 Encoder Decoder Encoder Decoder SRAM 1 SRAM 2 tag 12 140 Wa1 W1 Ra1 R1 Wa2 W2 R2 DataOUT Ra2 Control Logic Data Formatter 156 e Port data Valid Wa: Writeaddress Ra: Read address W: Writeenabled R: Read enabled Round Table Meeting

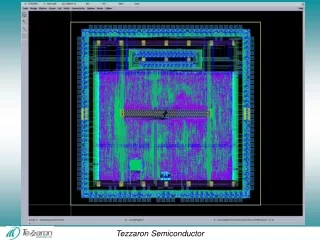

SRAM1 : a placed/routed config Round Table Meeting

SRAM1 : Write CONTROL LOGIC Time before a data is written in memory : #2.5 clock period reduce to 1.5 clock period Round Table Meeting

SRAM1 : Read Time before a data is read in memory : #2.5 clock period reduce to 1.5 clock period Round Table Meeting

Modifications • Modifications done : • Take off the flops to win 1 clock period (functionality of the block not changed) • Synthesis : a path is unconstrained (timing issue) • Size modifications for SRAM1 (to do): Mieczyslaw idea Round Table Meeting

SRAM1 : write (behaviour) Better than previous design : faster and smaller Round Table Meeting

SRAM1 : read (behaviour) Better than previous design : faster and smaller Round Table Meeting

To DO • #3 weeks to finish the blocks • Make transition with Mieczyslaw • Ensure the timing (current task) • Physical design • Assets: • Design flow: already gone through • Work environment (scripts, .lib, STA) : set Round Table Meeting

Thanks for paying attention Round Table Meeting

Back up Round Table Meeting

SRAM1 : Control (1/2) Block A Block J Module Encoder Module dataIN128 channels Module 7 7 7 address A address address J Mux A Mux Mux J read_address<10:0> 7 Décodeur d’adresses write_address<10:0> read_address 7 read_en write_address write_en Round Table Meeting

SRAM1 : Control (2/2) Hamming Dec3 32 152 Output block A 38 Hamming Dec2 152 32 Output block B dataOUT 38 152 Output block C Control Logic 140 38 ….. Hamming Dec1 32 152 38 Output block J Hamming Dec0 12 bits time stamps are added to the data in the Control Logic 32 Round Table Meeting

SRAM2 : Write NEED TO BE CHANGED as for SRAM1 Round Table Meeting

SRAM2 : Read NEED TO BE CHANGED as for SRAM1 Round Table Meeting