Lab 13 : Binary Counter Systems:

Lab 13 : Binary Counter Systems:. Slide 2. Three stage ripple counter. Slide 3. Down Counters. Slide 4. Up/Down Counters. Slide 5. Altera 4count Symbol. Input. J. J. J. Qc. Qa. Qb. 1. 1. 1. >Clk. >Clk. >Clk. K. K. K. Qc. Qb. Qa. 1. 1. 1. In. Qc. Qb. Qa. 0. 1. 2.

Lab 13 : Binary Counter Systems:

E N D

Presentation Transcript

Lab 13 : Binary Counter Systems: Slide 2 Three stage ripple counter. Slide 3 Down Counters. Slide 4 Up/Down Counters. Slide 5 Altera 4count Symbol.

Input J J J Qc Qa Qb 1 1 1 >Clk >Clk >Clk K K K Qc Qb Qa 1 1 1 In Qc Qb Qa 0 1 2 3 4 5 6 7 0 1 1 1 0 0 0 1 0 1 1 0 0 0 1 1 0 0 0 1 1 0 0 1 1 1 2 Qa 3 4 Qb 5 6 7 Qc Lab 13 : Three Stage Ripple counter : JK flip flops connected in the toggle mode can be connected together to create a binary counter system. Start with one JK flip flop, apply a clock waveform and sketch the Q output response. Assume PRE and Clr has been disabled (=1) on all flip flops. Qa will toggle on each negative edge of the input clock. Qb will toggle on each negative edge of Qa. Connect a second stage to output Qa. Qc will toggle on each negative edge of Qb. Connect a third stage to output Qb. Label the input clock pulses from 0 to 7 and place the counter response in a table. The table is called a COUNT state table. The counter is called a MOD 8 counter because it has 8 different count states. The counter restarts at 0, 0, 0 after clock input 7. MOD is short for the word MODULUS. Connect the flip flop outputs to 3 LED’s and you will see a binary count sequence from 0 … to … 7. The speed at which the counter counts is controlled by the input clock. 1 PPS input clock will display the 0 to 7 count sequence on the LED’s in 8 seconds. Each count state would last 1 sec. If the clock input was 1000 PPS then all 3 LED’s would appear to be constantly on at the same time. A count cycle would take 8milliSec. Too fast to be visible on the 3 LED’s. Slide #2

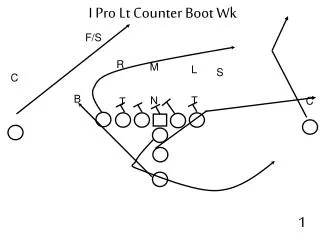

To make a counter count backwards all you need to do is to connect the Q to the Clk of the next flip flop. Input J Qa J Qb J Qc 1 1 1 >Clk >Clk >Clk K Qa K Qb K Qc 1 1 1 In Qc Qb Qa 0 0 0 1 0 1 1 0 1 0 1 1 0 0 1 0 1 1 0 0 0 0 1 1 1 1 2 Qa 3 Qb toggles on every negative edge of Qa. Qc toggles on every negative edge of Qb. Which is the same as the positive edge of Qb. 4 Qb Qa A negative edge on Qa is the same as the positive edge Qa. 5 6 7 Qc Lab 13: Down Counters : Qa toggles on every negative edge of the input clock. If you place the count states in a table you can see the down count sequence. Slide #3

1 0 Qa•1 1 0 Qb•1 J Qa J Qb J Qc 1 1 1 >Clk >Clk >Clk K Qa 0 0 K Qb 0 0 K Qc 1 1 1 1 0 Qa•1 0 1 Qb•1 0 1 Up/Down When the control input is high, the bottom AND gates pass the logic levels from the Q outputs. The top AND gates output 0. The OR gate outputs a Q•1+0 = Q. This connects Q to clock and the counter counts down or backwards. Lab 13: Up/Down Counter : This system combines the features of both an up and a down counter. The system has a count direction control input to select up counting or down counting. When the control input is low, the top AND gates will pass the logic levels from the Q outputs. The bottom AND gates output 0. The OR gate outputs a Q•1+0 = Q. This connects Q to clock and the counter counts up or forward. Slide #4

Step 1:Assert load and place number at inputs Step 5: Apply 4 clock pulses Step 1:Place number at inputs Step 4: Enable down counting 4count LDN 0 1 A 0 0 B QA 1 1 6 6 C QB 1 1 D QC 0 0 CIN QD DNUP COUT 0 1 SETN Step 2: Assert SETN Assert CLRN 0 0 1 0 100 0 11 0 0 100 0 11 0 CLRN 1 CLK Step 2: Assert Clock Lab 13: Altera 4Count Symbol: The Altera 4count symbol is a 4-bit counter system. Apply a pulse waveform to the positive edge triggered clock input and it counts from 0 to 15. Synchronous Load: LDN and ABCD and Clock: LDN=0 loads a number into Qa, Qb, Qc, Qd from A, B, C, D on positive edge of clock. LDN=1 disables the load feature. Clock is used for counting. The animation will demonstrate how to load the number 6 into the counter. Step 3: Apply 4 clock pulses Step 1: Disable load and clear inputs Step 2: Enable up counting Asynchronous Load: SETN and ABCD: SETN=0 loads a number into Qa, Qb, Qc, Qd from A, B, C, D immediately. The clock is not required. SETN =1 disables the load feature. Clock is used for counting. The animation will demonstrate how to load the number 6 into the counter. 0 000 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 0 001 11 0 1 111 0 111 1 0 11 1 0 00 0 11 0 0 0 11 0 0 010 0 1 00 0 000 0 001 0 010 0 01 1 0 1 0 1 0 0 1 0 0 0 1 1 0 0 0 0 0 100 0 01 1 0 100 0 0 0 1 Asynchronous Clear: CLRN: CLRN=0 resets (clears) Qa=Qb=Qc=Qd =0. Clock not required CLRN =1 disables the clear feature. Clock is used for counting. Count Direction: DNUP: DNUP=0 Counter counts forward or up (0,1,2…). DNUP=1 Counter counts backwards or down (15,14,13…). The animation will demonstrate an up count sequence to 4 and then a down count sequence back to 0. The count sequence can be reversed at any time. CIN and COUT: Carry in and Carry out are used to cascade counter symbols.Cascading will be explained in an upcoming lab. Altera Default Values:Altera connects LDN, SETN, CLRN, DNUP and CIN to 1 if they are left unconnected in a drawing. These are called default values. The default values will make the counter count down and disable the loading and clearing functions. Slide #5