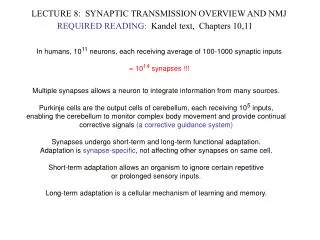

Lecture 8 Overview

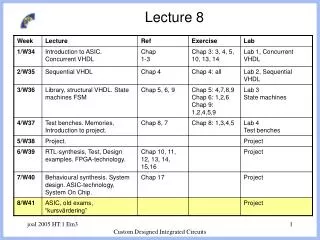

Lecture 8 Overview. Review of Combinational Logic Technologies Logic Implementation Programmable Logic Devices. Simple gate summary. The XOR gate. C = A XOR B C=A B. C. Exclusive OR The output is TRUE only if one or the other, but not both, inputs are TRUE Symbol is . The XNOR gate.

Lecture 8 Overview

E N D

Presentation Transcript

Lecture 8 Overview • Review of Combinational Logic Technologies • Logic Implementation • Programmable Logic Devices ENGN3213: Digital Systems and Microprocessors L#8

Simple gate summary ENGN3213: Digital Systems and Microprocessors L#8

The XOR gate C=AXORB C=AB C • Exclusive OR • The output is TRUE only if one or the other, but not both, inputs are TRUE • Symbol is ENGN3213: Digital Systems and Microprocessors L#8

The XNOR gate C=ANORB C=AB C • Inverse of XOR • The output is TRUE only if both inputs are the same. • "logical equality” ENGN3213: Digital Systems and Microprocessors L#8

CMOS gates • Gates are very easy to build using MOSFET transistors (recall; transistors can be considered as a voltage controlled switch) • p-type conduct when the input=0 • n-type conduct when the input=1 ENGN3213: Digital Systems and Microprocessors L#8

CMOS NAND gate • NAND gates are built using 4 MOSFETs • p-type conduct when the input=0 • n-type conduct when the input=1 ENGN3213: Digital Systems and Microprocessors L#8

Review of Gate Processing A NOT gate inverts its single input An AND gate produces 1 if both input values are 1 An OR gate produces 0 if both input values are 0 An XOR gate produces 0 if input values are the same A NAND gate produces 0 if both inputs are 1 A NOR gate produces a 1 if both inputs are 0 ENGN3213: Digital Systems and Microprocessors L#8

Can combine gates • To make different logic outputs A out B ENGN3213: Digital Systems and Microprocessors L#8

Logic Types • Positive Logic (active high) • 0 = 0 V., 1 = 1.0 V. • Negative Logic (active low) • 0 = 1.0 V., 1 = 0 V. • Mixed-Logic – logic with: • Negative (positive) logic inputs • Positive (negative) logic outputs • Arbitrary mixture of positive & negative logic ENGN3213: Digital Systems and Microprocessors L#8

Positive vs Negative Logic A Out B • In order for the Output of an AND Logical Function to be TRUE: input A AND input B must both be TRUE. This is Positive Logic. • Using the Same Function -It is also correct to say: If either input AOR input B (or both) is NOT TRUE the Output Will be FALSE. This is Negative Logic. ENGN3213: Digital Systems and Microprocessors L#8

Multiple Gate Interpretations • Positive logic: Negative logic: ENGN3213: Digital Systems and Microprocessors L#8

SOP and POS • Any logical expression can be reduced to either a "Sum-of-Products" form or a "Product-of-Sums" form ENGN3213: Digital Systems and Microprocessors L#8

DeMorgan's Theorem Proof "break the line, change the sign" Duality between AND and OR means that any logic function can be implemented by using just OR and NOT gates (NOR) , or by just AND and NOT gates (NAND) ENGN3213: Digital Systems and Microprocessors L#8

CMOS NAND gate • The NAND gate is by far the most important • It is cheapest to construct • It can be used to produce all other logic operations ENGN3213: Digital Systems and Microprocessors L#8

CMOS NAND gate • The NAND gate is by far the most important • It is cheapest to construct • It can be used to produce all other logic operations XOR ENGN3213: Digital Systems and Microprocessors L#8

NAND Gate Implementation • De Morgan’s law tells us that is the same as • By definition, is the same as • All sum-of-products expressions can be implemented with only NAND gates. ENGN3213: Digital Systems and Microprocessors L#8

Use of DeMorgan’s Theorems to Transform Logic Gates ENGN3213: Digital Systems and Microprocessors L#8

Choice of Logic Realization • CMOS, nMOS, & TTL logic families • Fewer transistors in NAND/NOR gates than in AND/OR gates • NAND/NOR also faster than AND/OR • Gate substitution: Use 3-input AND gate instead of cascaded 2-input AND’s (faster) ENGN3213: Digital Systems and Microprocessors L#8

... derives truth table Combinational analysis ENGN3213: Digital Systems and Microprocessors L#8

Signal expressions F = ((X + Y¢) . Z) + (X¢. Y . Z¢) ENGN3213: Digital Systems and Microprocessors L#8

New circuit, same function Multiply out:F = ((X + Y’) . Z) + (X’ . Y . Z’)=(X . Z) + (Y’ . Z) + (X’ . Y . Z’) ENGN3213: Digital Systems and Microprocessors L#8

Any number of manipulations can yield equivalent circuits e.g. F = ((X + Y’)Z) + X’YZ’ Note: [X’YZ’]Z = 0 (X + Y’)X’YZ’ = 0 (X’YZ’)(X’YZ’) = X’YZ’ So, F = [(X + Y’) + X’YZ’][Z + X’YZ’] =(X + Y’ + X’)(X + Y’ + Y)(X + Y’ + Z’)(Z + X’)(Z + Y)(Z + Z’) =(1)(1)(X + Y’ + Z’)(X’ + Z)(Y + Z)(1) = (X + Y’ + Z’)(X’ + Z)(Y + Z) Circuit: ENGN3213: Digital Systems and Microprocessors L#8

Another example: Push bubbles to obtain cancellations ENGN3213: Digital Systems and Microprocessors L#8

Another example: Push bubbles to obtain cancellations ENGN3213: Digital Systems and Microprocessors L#8

Conclude: given circuit ==> many equivalent equations circuit does not determine equation ENGN3213: Digital Systems and Microprocessors L#8

Two-level AND-OR Two-level NAND-NAND Three-level equivalent Also, equation does not determine circuit: ENGN3213: Digital Systems and Microprocessors L#8

Combinational analysis given circuit, determine function Combinational synthesis given function, determine circuit ENGN3213: Digital Systems and Microprocessors L#8

Design Considerations • In addition to logic functions, a designer must be concerned with a number of physical characteristics of digital logic circuits, including the following: • Propagation delays • Gate fan-in and fan-out restrictions • Power consumptions • Size and weight. ENGN3213: Digital Systems and Microprocessors L#8

Programmable Arrays of Logic Gates • Until now, we learned about designing Boolean functions using discrete logic gates • We will now describe a technique to arrange AND and OR gates (or NAND and NOR gates) into a general array structure • Specific functions can be programmed • Can use programmable logic arrays (PLA) or programmable array logic (PAL) ENGN3213: Digital Systems and Microprocessors L#8

Programmable Logic Devices • PROM (Programmable Read-only Memory) • PLA (Programmable Logic Array) • PAL (Programmable Array Logic) • FPGA (Field-Programmable Gate Array) ENGN3213: Digital Systems and Microprocessors L#8

Programmable Logic Device • What is a Programmable Logic Device (PLD)? • an IC that contains large numbers of gates, flip-flops and registers that are interconnected on the chip • can be configured by the user to perform a logic function • less board space • smaller enclosures • faster and less costly assembly processes • higher reliability (fewer ICs and circuit connections => easier troubleshooting) ENGN3213: Digital Systems and Microprocessors L#8

Programmable Logic Device • Basic Ideas of PLD • A PLD consists of an array of AND gates and an array of OR gates • Each input feeds both a non-inverting buffer and an inverting buffer to produce the true and inverted forms of each variable. (i.e. the input lines to the AND-gate array) • The AND outputs are called the product lines • Each product line is connected to one of the inputs of each OR gate • Three fundamental types of standard PLDs: PROM, PAL, and PLA ENGN3213: Digital Systems and Microprocessors L#8

PALs and PLAs Pre-fabricated building block of many AND/OR gates (or NOR, NAND) "Personalized" by making or breaking connections among the gates Programmable Array Block Diagram for Sum of Products Form ENGN3213: Digital Systems and Microprocessors L#8

Internal Structures of PLD ENGN3213: Digital Systems and Microprocessors L#8

Programmable Read-Only Memory (PROM) • Each possible minterm AND gate is present (fixed AND) plane and configurable OR plane • Can use it to do address decoding • Can also be use to implement logic functions ENGN3213: Digital Systems and Microprocessors L#8

F0 = X'Y' F1 = X'Y F2 = XY' F3 = XY X Y Decoders • A decoder always has n inputs and 2noutputs. • n bit address for 2nbit word of memory • Given any input to a decoder, only one decoder output is 1. • From truth table, circuit for 2x4 decoder • Each output is a 2-variable minterm (X'Y', X'Y, XY' or XY) ENGN3213: Digital Systems and Microprocessors L#8

F0 = x'y'z' F1 = x'y'z F2 = x'yz' F3 = x'yz F4 = xy'z' F5 = xy'z F6 = xyz' F7 = xyz x y z Decoders • Design a 3x8 decoder. ENGN3213: Digital Systems and Microprocessors L#8

0 1 2 3 4 5 6 7 decoder inputs Implementation of ROMs • ROM can be implemented using orthogonal arrangement of wires • optional connection at each intersection • decoder puts logic ‘1’ on exactly one of the horizontal wires - this can be detected at output if connection present • Some PROMs are configured by breaking connections • high voltage placed across one input and one output at a time • high current flow causes “fuse” at intersection to “blow” • Other PROMs can be erased and reprogrammed (EPROMs) • stored functions • m(0,1,3,4,6), m(0,1,3,5,7), m(2,3,6,7), m(0,3,4,6) ENGN3213: Digital Systems and Microprocessors L#8

0 A B C D 1 A B C D F 1 2 A B C D 3 A B C D 4 A B C D 5 A B C D 6 A B C D Enb 4:16 A B C D 7 dec 8 A B C D F 2 9 A B C D 10 A B C D 1 1 A B C D 12 A B C D 13 A B C D 14 A B C D F 3 15 S S S S A B C D 3 2 1 0 A B C D Decoder as a Logic Building Block Example Function: F1 = A' B' C D + A' B C' D + A B C D F2 = A B C' D' + A B CD' + A B C D F3 = (ABC D)' ENGN3213: Digital Systems and Microprocessors L#8

configurableconnection x0x2x3x4x5 x0x1x2x3x4x5 x0x2x4x5 x0x1x2x5 configurableconnection x0x4x5 x1x2x3x4 x0 x1 x3 x4 x5 x2 z0 z1 z2 z3 = x0x1x2x3x4x5 + x0x1x2x5 Programmable Logic Arrays • PLAs have configurable “AND-plane” & “OR-plane” • Can implement any 2-level AND-OR circuit • Efficient physical implementation in CMOS ENGN3213: Digital Systems and Microprocessors L#8

x0x2x3x4x5 x0x1x2x3x4x5 x0x2x4x5 configurableconnection x0x1x2x5 x0x4x5 x1x2x3x4 x0 x1 x2 x3 x4 x5 z2 = x0x2x3x4x5 + x0x1x2x3x4x5 z0 z1 Programmable Array Logic(Limited PLA) • PAL is similar to PLA but fixed OR-plane • Simpler to program and cheaper implementation • Limited number of terms in each output ENGN3213: Digital Systems and Microprocessors L#8

Alternative Representations Short-hand notation so we don't have to draw all the wires! A B C D F1 F2 F3 Notation for implementing F0 = A B + A' B' F1 = C D' + C' D F0 ENGN3213: Digital Systems and Microprocessors L#8

Field Programmable Gate Arrays • FPGA roots are in the CPLDs of the 1980's • Invented by Ross Freeman (co-founder of Xilinx) in 1984. • FPGAs can be used to construct more complex circuits • Applications of FPGAs include DSP, aerospace, defense systems, computer vision, speech recognition, cryptography etc. • FPGAs especially find applications in any area or algorithm that can make use of the massive parallelism offered by their architecture. • Chip contains a large number (1,000s to 100,000s) of configurable building blocks • CAD tools map high level circuit to basic blocks, configuring function generators & other configurable elements as needed ENGN3213: Digital Systems and Microprocessors L#8

FPGA • An FPGA contains both logic blocks and programmable routing (interconnects) • A logic block is a circuit block that is replicated in an array in an FPD • A logic block consists of clusters of logic cells • Each logic cell contains a Look up table (LUT). • They are called Configurable Logic Blocks (CLB) by Xilinx. • based on Look-Up Tables. Most commercial FPGAs have 4-input LUTs • The logic blocks of most SRAM-based FPGAs consist of logic cells • A logic cell consists of a LUT, a flip flop, and connection to adjacent cells. • A logic slice consists of 2 logic cells. • Xilinx counts closer to 2.25 logic cells per slice because they can do more per configurable logic block (CLB) than other architectures ENGN3213: Digital Systems and Microprocessors L#8

switch matrix wire segments configurable logic blocks (CLB) IO blocks (IOB) Xilinx FPGA Organization • CLBs can be connected to passing wires • Direct lines (DL) allow signal between adjacent CLB • DL can be programmed to connect to long wire segments • Long wire segments used to connect distant CLBs • Wire segments connected by switch matrix • Configuration information stored in SRAM bits that are loaded when power turns on ENGN3213: Digital Systems and Microprocessors L#8

0 01234567 0123 0 1 ABC 0 f(A,B,C) 1 1 0 1 1 0 configuration memory 1 Configuring Logic • Lookup table implements logic functions • Multiplexors and pass transistors implement routing • Switch matrix contains configurable clusters of pass transistors • provides wide variety of routing options ENGN3213: Digital Systems and Microprocessors L#8

MainFunctionGenerators CLK EC S/R LUT4 LUT4 Y D D PRE PRE S/R C G1G2G3G4 > > EC EC CLR CLR LUT3 YQ DIN H1 1 F1F2F3F4 XQ S/R C MainFunctionGenerators 1 X Xilinx Configurable Logic Block Clock EdgeSelect Set/ResetControl Clock EnableControl Flip Flop ENGN3213: Digital Systems and Microprocessors L#8

Things You Should Know • ROMS • Each possible minterm AND gate is present (fixed AND) plane and configurable OR plane • how large a ROM is needed for given set of logic equations? • PLAs • Limited number of AND gates • Programmable AND and OR gates. • PALs • Programmable AND plane • how are logic functions represented? • FPGAs • components of FPGA and how they relate to each other • components of typical logic cell (Configurable Logic Block) • how circuits can be mapped onto CLBs ENGN3213: Digital Systems and Microprocessors L#8