Nios TM 2.0

Nios TM 2.0. Altera’s embedded Processor Solution. Nios Embedded Processor. Configurable Soft Core Embedded Processor Optimized for Altera ® Programmable Logic Device (PLD) Architecture 32-Bit RISC Architecture License & Royalty Free Over 6,000 Kits Sold. Nios Device Support.

Nios TM 2.0

E N D

Presentation Transcript

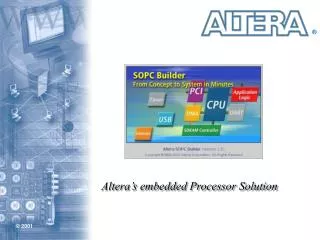

NiosTM 2.0 Altera’s embedded Processor Solution

Nios Embedded Processor • Configurable Soft Core Embedded Processor • Optimized for Altera®Programmable Logic Device (PLD) Architecture • 32-Bit RISC Architecture • License & Royalty Free • Over 6,000 Kits Sold

Nios Device Support Device Family Features Stratix™ Highest Speed (0.13-µm, All-Layer Copper) DSP Blocks Very High Speed I/O Very High Density Mercury™ Very High-Speed I/O with Clock-Data Recovery (CDR)Medium Density ARM®-Based Excalibur High SpeedMulti-Processor Systems (ARM + Nios)Medium-to-High Density APEX™ II High-Speed Differential I/OVery High Density APEX 20KEAPEX 20KC High-Speed Differential I/OLow-to-High Density FLEX® 10K Low CostLow-to-Medium Density ACEX® 1K Low CostLow Density

Combines Altera Strengths Robust IP Offerings Processor DSP Communication Bus Interface • High-Density, High-Performance Devices • Stratix • APEX II • Mercury • ARM-Based Excalibur • HardwareDevelopment Tools • Quartus® II • LeonardoSpectrum™ • ModelSim® • Development Boards SOPC Builder • Software Development Tools • Compiler • Debugger • RTOS

A powerful friendly GUI Hardware Environment Software Environment HardwareTeam SoftwareTeam Simulation Environment

The NiosTM System Architecture User Tri_State Device Nios Flash Nios SRAM @decoder Tri-State Bridge UART 0 InterruptControler Port Interface UART n Arbiter Arbiter Arbiter Arbiter Arbiter Timer 0 Timer n Wait StateGeneration OCD SPI 0 SPI n GPIO 0 GPIO n Data InMultiplexer DMA 0 STRIPE DMA n AMBA / AVALON MemoryInterface DynamicBus Sizing User-DefinedInterface AVALON (Bus Peripheral Module)

SOPC Builder Ready Components ARM922T™Processor DMA USB 1.1 SDRAM Nios™ Embedded Processor PCI USB 2.0 SSRAM ARM®-to-Nios Bridge (AMBA AHB-to-Avalon) GPIO SPI SRAM Interface to User Logic Timer CAN 2.0 FLASH 10/100 Ethernet Watchdog 16550S UART On-Chip ROM On-Chip RAM The List Keeps Growing . . .

A Lego's like system Peripherals Available Options The 2.0 CPU core

A modular generation Software Environment Hardware Environment Netlist Generation Simulation Environment Sources for the Synthesis and simulation are available in both VHDL and verilog languages. All PLD families supported

NiosTM Hardware Description 1- The Core, 2- Custom Instruction 3- Multi-Mastering

NiosTM processor Features 1/2 • 32-Bits or 16-Bits RISC Architecture • 5 Stage Pipeline • Fully-Synchronous Interface • Same 16-bits instruction Set for both Data Path sizes. • Windowed Register File • Configurable to 512 Registers. • Fast Context Switching. • Integrated Interrupt Controller • 64 Vectored Interrupts. • Selectable Reset Address

NiosTM processor Features 2/2 • Dynamic Bus Sizing mechanism • Arithmetic's functions for the ALU. • Fixed Barrel-Shifter that executes all shift instructions in 2 clock cycles, regardless of the shift-distance. • MSTEP multiplier or 16x16 Bits multiplier. • Optimized Data Processing • Custom CPU Instructions • >2X Acceleration (e.g. MAC, MP3, Bit Swap) • Optimized Data Flow • Simultaneous Multi-master Bus Capability • Gbps Throughput

Nios RISC Processor Block Diagram • Standard RISC Components • Fully-Synchronous Interface • Native Verilog • Native VHDL

Custom Instruction Block Diagram Optional FIFO, Memory, Other Logic Nios System Module • Extends Nios Instruction Set • Up to 5 Instructions • System Builder: • Adds User Logic to Nios ALU • Assigns Op-Code • Generates C & Assembly Macros • Profiler Tools.

Traditional Data Flow for Multi-Masters DMA (Master 2) • Direct Memory Access (DMA) • Processor Waits For Bus During DMA Masters System CPU (Master 1) Bottleneck Arbiter Determines Which Master Has Access To Shared Bus DMA Bus Arbiter DMA Arbitor System Bus I/O 1 I/O 2 Data Memory Program Memory Slaves

Simultaneous Multi-Master Avalon Bus Master 1 (Nios CPU) Master 2 (100Base-T) I D Masters Avalon Bus Avalon Bus Slaves Arbiter • Multiple Arbitration • Schemes • Round Robin • Priority Based I/O 1 I/O 2 Data Memory 1 Program Memory

Simultaneous Multi-Master Bus Multi-Master Avalon Master 1 (Nios CPU) Master 2 (100Base-T) Master n (100Base-T) I D Masters Avalon Bus Avalon Bus Avalon Bus Arbiter Arbiter Slaves I/O 1 I/O 2 Data Memory 1 Data Memory n Program Memory

Simultaneous Multi-Master Bus Master 1 (Nios CPU) Master 2 (100Base-T) Master n (100Base-T) I D Fetch Code Receive Packets Send Packets Avalon Bus Avalon Bus Avalon Bus Arbiter Arbiter I/O 1 I/O 2 Data Memory 1 Data Memory n Program Memory

DMA Peripheral support Master 1 (Nios CPU) Master 2 (SPI) DMA I D Avalon Bus Avalon Bus Arbiter I/O 1 I/O 2 Data Memory 1 Program Memory

SOPC Builder Design Flow Hardware HDL Simulation Software Header File Custom Library OS Kernel SignalTap™ Logic Analysis Debug/Profile Download Download Define System CPU Peripherals Memory User Logic Generate Application Hardware Simulate Application Software Finished System

Memory Device Simulation Models • Applies to the following Nios Memories • On Chip Memory (ROM or RAM) • SRAM (one or two IDT71V016 chips) • Flash Memory Source files (*.c & *.s) are compiled. Data files (*.mif & *.srec) are converted File is used in raw format Useful for non-standard build eg nios-build –cc –O0 hello.c String is used in raw format

UART Simulation • UART rx and tx transmissions are echoed to ModelSim Console

RTL Simulation Start ModelSim • Nios SOPC Builder Automatically creates simulation model plus • ModelSim Project • Testbench • Simulation Scripts • Formatted Wave Window

Nios TestBench Nios Flash Nios SRAM Nios 32 Bit RAM User Tri_State Device Included Not Included Data (32) Address (32) Nios Processor Tri-State Bridge SDRAM Controller SDRAM Address (32) 32-BitNiosProcessor Clock Read Avalon Bus Write PIO User Device Reset Data In (32) Data Out (32) SPI User Device User-Defined Peripheral User Device On Chip ROM IRQ IRQ #(6) User-Defined Interface User Peripheral On Chip RAM UART Timer User Device

Simulation Scripts • When ModelSim is started from the SOPC Builder a set-up script is run automatically which creates aliases for simulation scripts • The set up script can be run independently as follows: • do setup_sim.do • Simulation Scripts • sCompiles HDL source code and loads design • cRebuilds memory contents based on software code Includes changes since Nios generation • w Opens Wave window with “useful” signals Will have to add user signals • h Displays help message describing scripts

Wave Window • Adds UART and CPU signals by default • CPU Opcodes are decoded and displayed to help trace software execution

Nios Debug Solutions Provider Product Description Viosoft Arriba! IDE with Integrated Support for Nios On-Chip Debug Module - Hardware Breakpoints & Processor Trace Microtronix Debugger Module External Memory Daughter Card for Use as Software Trace Capture Buffer Redhat GDB / Insight * Software Debugger Altera Tracelink * Interface to Nios On-Chip Debug Module Hardware Breakpoints & Processor Trace * Included in Excalibur Development Kit Featuring Nios Processor

Red Hat GNU Debugger (GDB) • Run Control • Breakpoints, Watchpoints, Catchpoints • Stack Frame Analysis • List & Search Source Files • Examine Memory, Constants, Variables • Disassemble Machine Code • Examine Expressions Using C / C++ Operators

Red Hat Insight Debugger • Graphical User Interface for GDB • Windows • Source • Stack • Register • Memory • Watch Expression • Local Variables • Breakpoints • Console • Function Browser

Altera Tracelink • Baseline Support for Nios Processor Ver. 2.0 On-Chip Debug & Software Trace Capabilities • Captures Instructions and Data Executing in Nios CPU • Up to 1.2 Million Instructions • Captures Trace Data at Full System Speed • Uses External Trace Memory Debugger Module • Available from Microtronix

Hardware for Trace • Enable On-Chip Debug Logic in SOPC Builder • Connect Nios OCD Ports to External Memory on Debugger Module Nios System Module Program Memory Simultaneous Multi-Master Avalon Bus O C D Nios CPU UART Other…

Nios Ethernet Development Kit • Supports Wide Range of Applications • Factory Floor Automation • Basic Ethernet Connectivity • Internet Upgradeable Hardware • Supports All PLD Families • Development Board • External 10Mbyte MAC/Phy • Support for 2 Ports • Software Included • TCP/IP Stack • Reference Design • Hardware (Quartus™ Project) • Software (Web Server Application) • Price $495

What do you get in the LDK box? µCLinux kernel source code Three daughter boards to enable Linux development on NDK board Memory Expansion: SDRAM & flash OS Support: Real-time Clock & IDE interface Ethernet Connectivity: NEDK daughter card Serial Y-cable for debug Software & reference application Web server Linux command shell µCLibC & Kernel open source Hardware reference design Linux works out of the box, no Quartus compile necessary Open Source. No licensing fees. No Royalties. List Price: $2,495 Operating System Support Board Ethernet Connectivity Board Memory Expansion Board

PCI32 Nios Target MegaCore® Function • PCI Interface to Nios via Avalon™ Bus Bridge • Nios System Builder Interface • Behavioural Simulation Models • PCI Testbench for PCI32 Nios Target Core • Low-Level Driver Routines in C Source Code for Nios Embedded Processor • Reference Design for Use with Nios Embedded Processor • Complete Documentation

Nios™ OS / RTOS Support Provider Product Description Accelerated Technology Nucleus PLUS Royalty-Free, Source-Available RTOS Mapusoft Technologies OSChanger Tool to Convert pSOS / VxWorks Applications to Nucleus PLUS Microtronix µCLinux Open-Source OS Shugyo Design KROS Small-Footprint, Royalty-Free, POSIX-Compliant RTOS

Nucleus PLUS • Multi-Tasking Real-Time Kernel • Priority, Pre-Emptive Scheduler • Inter-Task Communication • Pipes, Queues, Mailboxes • Inter-Task Synchronization • Semaphores, Signals, Events • Memory Management • Fixed or Variable • Dynamic Creation/Deletion of All Objects

uCLinux • Linux Development Kit • Software • Linux Kernel & uClibc Library – Nios™ Port • Nios Linux Driver Support • 70+ Applications • 30-Day Installation Support • Hardware • 10BaseT Ethernet Card • Operating System Support Board • CompactFlash Connector • Real-Time Clock • IDE Interface • SDRAM/Flash Expansion Board

To add or set up the Software Components, you need to go to the More “[cpu module]” Settings Tab. The Software Components section on this page will look a lot like the System Contents page (first image) but with software instead of hardware components. The functionality is the same.

The first of several pages will show up. All the typical options for configuring the kernel are presented as a list of radio buttons and/or checkboxes. Once the settings are finished, they are saved and ready to be used during the compile process. The final screen will present the “Microtronix Make Console”.

Since this is a new project, there is no actual source tree for us to compile. The source code repository files (included with the Microtronix Software Component) need to be copied. The files are copied by clicking the “Copy Files” button. Assuming this is cpu component “nios_0”, the source tree will be copied to the “Altera Projects\Excalibur\nios_0\uClinux” directory.

Once the Copy Files button has been pressed, a small console will pop up and begin the copying of files. The “Make Dependencies” button will now be enabled and ready for use. After the copying is done, pressing the Make Dependencies button will cause a “make clean” command to be executed followed by the “make dep”.

Once finished, the file “linux.srec” will be ready for you to upload to your Excalibur Board.

KROS Real-Time Operating System Features Tiny Footprint, 16K to 64K POSIX Interface GNU Compiler Support Supports Altera Nios CPU Advantages Low Cost Source Code Provided Royalty Free