Queue Manager

Queue Manager. Yuhua Chen, Wen-Jing Tang Applied Research Lab Washington University October 5, 2014. MSR RAD Block Diagram. QMGR Top. CARL/QMGR Interface. QMGR/OSAR. QMGR/CCP Interface. QMGR/PSM Interface. QMGR Block Diagram. CCP. Free Pointer Controller. 16. 36. 96. 96.

Queue Manager

E N D

Presentation Transcript

Queue Manager Yuhua Chen, Wen-Jing Tang Applied Research Lab Washington University October 5, 2014

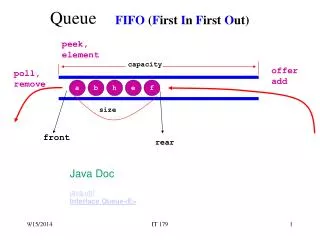

QMGR Block Diagram CCP Free Pointer Controller 16 36 96 96 SRAM Arbitrator 32 Queue Length Controller (QLNC) 36 Line Queue Manager (LNQM) 32 36 SRAM CARL 48 DISPATCHER (DCHR) Queue Header Controller (QHDC) 36 48 36 Switch Queue Manager (SWQM) 32 36 36 36 OSAR 16 Output Controller (OUTC) LC PSM 32 16 SW PSM 32

DCHR (Dispatcher) Single Copy Packet • Dispatch packet headers to proper processing blocks • Recognize SPC return packets and adjust QID accordingly • Keep track of Header Only return packets • Process multiple copy packets Multi Copy Packet Common Reference

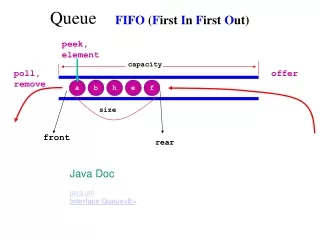

SRAM Arbitrator Functions • Manage SRAM bandwidth • Arbitrate among all requesting units • Free PTR CTRL: 1 cycle, Read/Write • Common Ref: 1 cycle, write only • SWQM enqueue: 2 cycles, write only • SWQM dequeue: 2 cycles, read only • LNQM enqueue: 2 cycles, write only • LNQM dequeue: 2 cycles, read only • OUTC: 1 cycle, Read/Write • zero cycle turn around among different units

SRAM Arbitrator Write Timing One-Cycle Write Two-Cycle Write

SRAM Arbitrator Read Timing One-Cycle Read Two-Cycle Read

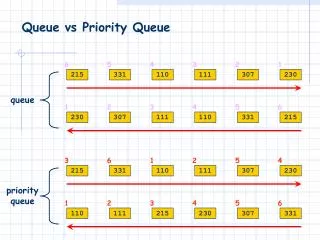

Queue Manager Artichecture Reserved flows To Output 0 . . . 0 0 To LC Datagram flows … … To SW Port 0 Line Card QMGR To Output 7 … Port 0 Switch QMGR … 7 7 Port 7 Port 7 Switch QMGR Line Card QMGR

Per Output Queue Table (SWQM) External SRAM Packet Headers Output Queue Table

Line Card Queue List (LNQM) Queue Headers Packet Headers Current Queue Previous Queue Queue Header Table (on-chip Block RAM) External SRAM

QLENC Functions • Keep track of per flow queue length • Respond to queue length inquiry from CCP • Respond to queue length inquiry from LNQM • Packet Drop Policy will be implemented here

Free PTR CTRL Functions • Manage External SRAM space • Initialize free pointer list • Maintain free pointer list • Handle free pointer fetch & return • Maintain on-chip free pointer cache • Recycle free pointers locally

OUTC Functions • Send outgoing packet headers to SW/LC OSAR FIFO • Send drop packets to SW/LC PSM drop FIFO • Process multiple copy packets • Obtain packet pointer • Update Copy Count