CMOS periphery

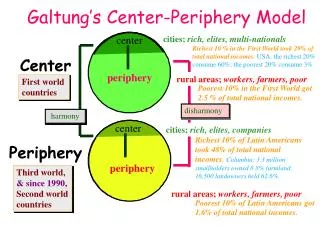

CMOS periphery. CMOS p eriphery: detector types. Embedded pixel sensor With readout cells on the periphery With readout cells in the active region With continuous readout With trigger readout Segmented strip detector with hit-buffer based multiplexing With/without digital z encoding

CMOS periphery

E N D

Presentation Transcript

CMOS periphery: detector types • Embedded pixel sensor • With readout cells on the periphery • With readout cells in the active region • With continuous readout • With trigger readout • Segmented strip detector with hit-buffer based multiplexing • With/without digital z encoding • Segmented strip detector with lossyconstant-delay-multiplexing (readout latency only 80ns) • With/without digital z encoding

HVCMOS sensor types Type A – smart diode Type B – HVMAPS CMOS CMOS PMOS must be isolated with a deep P-well N-Well N-Well N-Well Variant 1 PMOS not isolated Variant 2 PMOS isolated with a deep P-well N-Well CMOS N-Well CMOS N-Well

Readout types: in-pixel hit processing (embedded pixel sensor) Concept: Every pixel has its own readout cell, placed on the chip periphery CSA Hit flag Comparator Priority scan logic RAM/ROM Pixel contains a charge sensitive amplifier and optionally a discriminator with a threshold tune DAC Comparator and Thr tune DAC Read Time stamp Data bus Readout cell function – time stamp is stored when hit arrives Hit data are stored until the readout Priority logic controls the readout order RO cell size in 0.18um ~ 7um x 40um (with comparator and thr-tune DAC) Without comparator: 7um x 20um Example: Pixel size 80um x 320um Chip size: ~ 2cm x 2cm Number of pixels: 256 x 64 Size of periphery with comparators: 2cm x 224um (1.12%) Size of periphery without comparators: 2cm x 112um (0.6%) One RO cell /pixel RowAddr + TS Shift register in-pixel hit processing Matrix size M x N Output data width ln(N)=n+TS Periphery ~ 1% - 1.5%

Readout types: in-pixel hit processing with trigger (embedded s.) Concept: Every pixel has its own readout cell, placed on the chip periphery CSA Triggered hit flag Comparator Hit flag RAM/ROM Priority scan logic Pixel contains a charge sensitive amplifier and a discriminator with threshold tune DAC Time stamp Delayed TS and trigger Read Data bus One RO cell /pixel Readout cell function – time stamp is stored when hit arrives The stored time stamp is compared with the current time stamp If trigger arrives with the correct latency, the triggered hit flag is set Priority logic controls the readout order Estimated cell size in 0.18um without comparator ~ 7um x 40um Example: Pixel size 80um x 320um Chip size: ~ 2cm x 2cm Number of pixels: 256 x 64 Size of periphery without comparator: 2cm x 224um (1.12%) RowAddr + TS Shift register In-Pixel hit processing Matrix size M x N Output width n+TS Periphery ~ 1.5%

In-pixel hit processing with the RO placed in active area Concept: Every pixel has its own readout cell, placed in the pixel itself (active area) Triggered hit flag Smart diode implementation Hit flag RAM/ROM CSA Comparator Priority scan logic N-Well Time stamp Delayed TS and trigger Read Data bus The implementation of the whole readout in active region requires deep P-Well No digital periphery required

In-pixel hit processing with the RO placed in active area HVMAPS implementation N-Well N-Well N-Well

Segmented strip detector with hit-buffer based multiplexing CSA Comparator hit Hit sr ff Pixel Ck hit EoC buffer 25ns clock synch 1 Write prio. logic TS Read prio. logic Full flag Data In FIFO Hit RAM Shift register Segmented strip Output width 1 + TS Small periphery (<1%) Pad-area dominates Hit TS Shift reg.

Segmented strip detector with hit-buffer based multiplexing CSA Comparator Address ROM hit Address RAM Address Hit sr ff Pixel Ck Sync Address, hit EoC buffer EoC buffer 25ns clock synch A few cells /column n Write prio. logic TS Read prio. logic Full flag Data In FIFO Hit RAM Shift register Segmented strip with digital row encoding Output width n+ TS Small periphery (<1%) Pad-area dominates Scrambled address when more than a hit/column Address Hit TS Shift reg. Data bus Read

Scheme that copes with hit multiplicity CSA Comparator AddressUp AddressDown Hit Pixel n n n n Shift register Segmented strip with digital row encoding Output width n+ TS Small periphery (<1%) Pad-area dominates Scrambled address when more than two hits/column

Column mapping Multiple hits/column possible due to charge sharing Multiple hits/column unlikely

Segmented strip detector with lossy constant-delay-multiplexing A B C D Output 1 Output 2

Segmented strip detector with lossy constant-delay-multiplexing A B C D Output 1 Output 2

Segmented strip detector with lossy constant-delay-multiplexing 0 A 1 B 2 C D Output 1 Output 2

Segmented strip detector with lossy constant-delay-multiplexing 0 A 1 B 2 C D Output 1 A Output 2 B

Segmented strip detector with lossy constant-delay-multiplexing A B C D Output 1 Output 2

Segmented strip detector with lossy constant-delay-multiplexing A B C D Output 1 Output 2

Segmented strip detector with lossy constant-delay-multiplexing 0 A B 0 C 1 D Output 1 Output 2

Segmented strip detector with lossy constant-delay-multiplexing 0 A B 0 C 1 D Output 1 C Output 2

Segmented strip detector with lossy constant-delay-multiplexing A B C D Output 1 Output 2

Segmented strip detector with lossy constant-delay-multiplexing A B C D Output 1 Output 2

Segmented strip detector with lossy constant-delay-multiplexing 0 A 1 B C D 2 Output 1 Output 2

Segmented strip detector with lossy constant-delay-multiplexing 0 A 1 B C D 2 Output 1 A Output 2 D

Segmented strip detector with lossy constant-delay-multiplexing A B C D Output 1 Output 2

Segmented strip detector with lossy constant-delay-multiplexing ROM FFs: 2304 Demux with en FF Addr 3-bit adder 8 3 in 1 f f f en m a inc 3 8 3 f 3 a f 3 8 8 3 chan Chan0-14 Addr 1 Pipeline structure 8 in 1 f f f en m a 8x8 inc f a f Segmented strip Output width 8x8 Constant delay Small periphery (<1%) Pad-area dominates Hit loss when more than 8 hits/BC a Chan15 Chan16-30

Segmented strip detector with lossy constant-delay-multiplexing n FFs: 6912 n f n f n f in n addr 3 in 1 f f f en a inc 3 8 3 f 3 a f 3 8 8 3 chan Chan0-14 n n f n f n f in n Pipeline structure 1 f f f en a 8x8 inc f a f Segmented strip with binary row encoding Output width 8x(8+n) Constant delay Small periphery (<1%) Pad-area dominates Hit loss when more than 8 hits/BC a Chan15 Chan16-30

Segmented strip detector with analog row encoding CSA Comparator Analog address-encoding Segmented strip with analog row encoding Analog z-encoding Output width m No periphery