3. 设置时间轴 ① 设置网格大小。 选择菜单命令 Option / Grid Size, 出现 Grid Size 对话框。

2.22k likes | 2.33k Vues

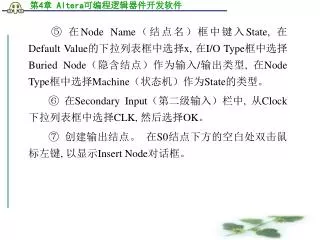

⑤ 在 Node Name (结点名)框中键入 State, 在 Default Value 的下拉列表框中选择 x, 在 I/O Type 框中选择 Buried Node (隐含结点)作为输入 / 输出类型 , 在 Node Type 框中选择 Machine (状态机)作为 State 的类型。 ⑥ 在 Secondary Input (第二级输入)栏中 , 从 Clock 下拉列表框中选择 CLK, 然后选择 OK 。

3. 设置时间轴 ① 设置网格大小。 选择菜单命令 Option / Grid Size, 出现 Grid Size 对话框。

E N D

Presentation Transcript

⑤ 在Node Name(结点名)框中键入State, 在Default Value的下拉列表框中选择x, 在I/O Type框中选择Buried Node(隐含结点)作为输入/输出类型, 在Node Type框中选择Machine(状态机)作为State的类型。 • ⑥ 在Secondary Input(第二级输入)栏中, 从Clock下拉列表框中选择CLK, 然后选择OK。 • ⑦ 创建输出结点。 在S0结点下方的空白处双击鼠标左键, 以显示Insert Node对话框。

⑧ 在Node Name框中键入Q[2 ..0], 在Default Value下拉列表框中选择0, 在I/O Type框中选择Output Node(输出)作为输入/输出类型, 在Node Type框中选择Registered(寄存器)作为Q[2 ..0]结点的类型。 • ⑨ 在Secondary Input栏中, 从Clock下拉列表框中选择CLK, 然后选择OK。

3. 设置时间轴 • ① 设置网格大小。 选择菜单命令Option / Grid Size, 出现Grid Size对话框。 • ② 键入20 ns 以设置20纳秒的网线间隔。 时间单位必须紧接在时间值之后(即它们之间没有空格)。 选择OK。 • ③ 设置时间轴长度。 选择菜单命令File / End Time, 出现End Time对话框, 键入1.0 μs作为文件的结束时间, 然后选择OK。 时间轴长度决定设计项目的状态循环周期。 网格大小和时间轴长度共同确定了波形设计项目一个循环周期内任一结点可能的状态数。

④ 显示网格。 选择菜单项 Option / Show Grid, 竖直网线就会以20 ns的间隔显示在波形编辑窗口中。 • ⑤ 使能网线的“磁(Magnetic)”属性。 打开选择菜单项Options / Snap to Grid, 以使参考线自动移动到附近的网格位置上。 • ⑥ 调整各显示区大小。 用鼠标左键按住域大小调整手柄, 并将其向左或向右拖动到合适的位置上, 以重新调整Name域、 Type域以及Value域的宽度。

4. 编辑输入结点波形 • 通过编辑输入激励波形提供输入向量。 在对某一项目进行编译项目时, 编译器根据输入结点与隐含结点和输出结点的逻辑电平的对应关系, 综合出设计逻辑。 编辑Mc项目结点波形的步骤如下: • ① 编辑输入结点Dir波形。 Dir用于控制步进电机的旋转方向。 在Dir波形的0 ns处按下左键, 拖动鼠标到500 ns处再松开, 即选中PE波形的0 ns~500 ns区间, 点击图形工具钮, 则将该区间段置为高电平。 再使用图形工具钮, 将Dir的500 ns~1.0 μs区间置为低电平。

② 编辑输入结点CLK波形。 CLK用于控制步进电机的步进旋转。 点击Name栏中的CLK,即选中整个CLK波形, 然后点击图形工具钮, 出现图4.53所示Overwrite Clock对话框。 选Starting Value 为0表示时钟起始状态为低电平, 选Multiplied By为2表示CLK波形的周期为当前的网格大小所允许的周期的2倍(40 ns×2)。

③ 编辑隐含状态机结点State波形。 State用于指示三相六拍步进电机的控制状态S0~S5。 选中State的0 ns~80 ns时间段, 然后点击图形工具钮, 出现图4.87所示Overwrite State Name对话框, 输入S0, 选择OK。 参照图4.88, 输入在Dir为高或为低时的控制状态S0~S5。 • ④ 编辑输出结点Q[2 ..0]波形显示方式。 双击Name栏中的Q[2 ..0], 在出现的Enter Group对话框中选择Bin项, 然后选择OK。

⑤ 编辑输出结点Q[2 ..0]波形。 对应于S0~S5, 控制状态输出应为001、 011、 010、 110、 100、 101。 选中State的0 ns~80 ns时间段, 然后点击图形工具钮, 出现图 4.88 所示Overwrite Group Value对话框, 输入001, 选择OK。 参照图4.89, 输入在Dir为高或为低时的其它输出状态。

⑥ 浏览编辑波形。 使用 、缩放波形局部, 使用 观察波形全景。 如果Value域过窄而不能显示出逻辑值或状态值, 则用破折号代替。 • ⑦ 确认编辑的正确性。 在Time域单击鼠标, 即出现时间参考线, 通过拖动时间参考线把柄把时间参考线相继移到每一个逻辑电平转换处。 选择菜单Utilities \ Find Next Transition也能达到同样的目的。 时间参考线移动时, Value域显示参考线所在位置的各个结点的逻辑电平或状态名都会在其中。

⑧ 选择 快捷钮, 再在参考线上单击鼠标, 可以获得在线帮助信息。 若不习惯用图形工具钮编辑波形, 可使用菜单命令Edit / Overwrite, 或在待编辑处右击菜单中选Overwrite命令来编辑波形。

5. 检查基本错误并创建一个默认的符号 • ① 浏览编辑波形。 使用、 缩放波形局部, 使用观察波形全景。 如果Value域过窄而不能显示出逻辑值或状态值, 则用破折号代替。 • ② 确认编辑的正确性。 在Time域单击鼠标, 即出现时间参考线, 通过拖动时间参考线把柄把时间参考线相继移到每一个逻辑电平转换处。 选择菜单Utilities \ Find Next Transition也能达到同样的目的。 时间参考线移动时, Value域显示参考线所在位置的各个结点的逻辑电平或状态名都会在其中。

③ 获得在线帮助信息。 选择 快捷钮, 再在参考线上单击鼠标。 • ④ 点击 快捷钮或选择菜单命令File / Save & Check。 • ⑤ 双击编译器标题条(菜单)左侧的编译器图标, 以关闭编译器窗口。 点击快捷钮, 确保Mc.wdf文件在前台显示。 • ⑥ 选择菜单命令File / Create Default Symbol, 当被问及是否要覆盖已存在的符号文件(.sym)时, 选择OK。 • ⑦ 再次关闭波形编辑器窗口。

6. 退出波形编辑器窗口 • ① 选择菜单命令File / Save或点击 快捷钮, 则保存图 4.89 所示的波形设计文件Mc.scf。 • ② 选择菜单命令File / Close或点击波形编辑器窗口的关闭钮, 以关闭波形编辑器窗口文件。 • ③ 编译、 仿真图 4.89 所示波形设计项目Mc.wdf。 仿真结果参考图 4.90。

4.3.4 编译控制 • MAX+PLUSⅡ编译过程包括语法检查、 网表提取、 逻辑综合、 器件及其资源配置(器件划分与布局布线)、 形成各种输出文件等。 其中, 逻辑综合和器件划分与布局布线这两个过程分别由编译器中的逻辑综合器及器件划分器完成。 MAX+PLUSⅡ提供了默认的相关配置以指导逻辑综合器及器件划分器的工作, 设计者也可以自己设定这些配置项, 使编译器按照自己的要求工作。 典型的逻辑综合及器件资源配置项有:

选定器件、 逻辑综合、 定时要求、 引脚锁定及合并(Clique)等。 所有这些配置项都存放在ACF文件中, 设计者可以通过对Assign菜单项操作来完成对ACF文件的修改、 编辑。 由于在4.2.3节已涉及过选定器件、 设置定时要求及引脚锁定等内容, 所以这一节主要介绍其余典型配置项的使用以及对ACF文件的操作。

1. 控制逻辑综合 • 逻辑综合操作是按照逻辑综合配置项要求, 在协调设计逻辑的空间占用、 速度及易适配性基础上对设计项目进行优化(化简)。 对逻辑综合的控制分为两级, 即局部逻辑级和全局逻辑级。 局部逻辑综合控制只影响局部逻辑综合, 即仅影响指定的引脚、 结点和逻辑块; 全局逻辑综合控制影响所有引脚、 结点和逻辑块。

1) 局部逻辑综合的控制 • 局部逻辑的综合由设计者选择的逻辑综合方式和局部逻辑配置选项共同确定。 • ① 高亮要选择的结点、 引脚或逻辑块。 • ② 选择菜单命令Assign / Logic Options, 进入Logic Options对话框, 如图 4.91 所示。 • ③ 在Logic Options下拉列表中选择所使用的逻辑综合风格。

④ 如有必要, 选择Define Synthesis Style...钮(参看后面), 定义所使用的逻辑综合风格。 • ⑤ 如有必要, 选择Individual Logic Options...钮(参看后面), 设置局部逻辑配置选项。 • ⑥ 选择Add及OK, 完成设置。

2) 设置局部逻辑配置选项 • 局部逻辑配置选项用于控制局部逻辑综合时是否使用一些器件结构特性及逻辑综合算法。 • ① 选择菜单命令Assign / Logic Options, 进入图4.91所示逻辑配置选项对话框。 • ② 点击Individual Logic Options...钮, 进入图4.92左侧所示局部逻辑配置选项对话框。

③ 选择需要打开的结构特性项或逻辑综合项。 图中, 灰色或Default项表示该项由高一级或全局逻辑综合控制来设定, 深色对号或Auto表示使能该特性项, 空白或Ignore表示禁止该项。 • ④ 若有必要, 可选择Advanced Options钮, 进入图4.92右侧所示对话框进行高级设置。 • ⑤ 选择OK, 完成设置。

3) 定义逻辑综合风格 • 逻辑综合风格是频繁使用的预先定义好的一组逻辑综合选项配置, 包括FAST、 NORMAL和WYSIWYG等三种。 用户可以根据设计需要选定一种风格或重新定义所选定的风格。 • ① 在图 4.91 所示逻辑配置选项对话框中, 或者在图 4.40 所示的全局逻辑综合对话框中选择Define Synthesis Style...钮, 进入图 4.93 所示的定义逻辑综合风格对话框。

② 选择要定义的风格并设置相关的特性项。 或者选择Use Default钮, 调入MAX+PLUSⅡ默认设置。 • ③ 根据需要, 可以选择Advanced Options钮进入图 4.93 右侧所示的高级选项对话框进行设置。 • ④ 选择OK, 完成设置。

4) 全局逻辑综合控制 • 全局逻辑的综合由设计者选择的逻辑综合方式和全局逻辑配置选项共同确定。 • ① 选择菜单命令Assign / Project Logic Synthesis, 进入图4.40所示全局逻辑配置选项对话框。 • ② 参照4.2.3节的第二部分, 在图4.40所示的全局逻辑综合对话框中选择预定义的逻辑综合风格NORMAL、 FAST、 WYSIWYG, 或者创建并选用用户自定义风格设置。 • ③ 根据需要设置全局逻辑优化策略以及其它结构特性项或逻辑综合项。

④ 选择OK, 完成设置。 • 5) 更多的控制逻辑综合的方法 • 对于FLEX器件, MAX+PLUSⅡ可以通过设置定时要求配置选项来综合出符合指定速度性能要求的逻辑。 也可以使用定时分析手段改进特定的延时路径, 以提高设计项目的速度性能。 定时要求配置分局部控制和全局控制。

① 局部控制: 高亮所选引脚, 选择菜单命令Assign / Timing Requirements, 设置所要求的tpd、 tco、 tsu及fmax。 • ② 全局控制: 选择菜单命令Assign / Global Project Timing Requirements, 设置所要求的tpd、 tco、 tsu及fmax。

2. 控制器件划分与资源配置 • 1) 关于器件划分与资源配置 • MAX+PLUSⅡ编译器的Partitioner(划分)模块可以自动地或者根据指定的要求, 进行器件划分和器件资源配置, 将设计项目装入单个或多个CPLD器件中。

用户可以使用图形、 文本或波形编译器中的Device Enter Assignments、 Clique Pin/MC/Chip命令在顶层设计文件中进行资源和器件配置, 也可以在顶层TDF的设计段中进行这些工作。 但是, 在一个设计项目中不要同时使用两种配置方法。 这些工作包括选择器件、 锁定(配置)引脚、 配置隐埋的宏单元、 使用合并项对影响速度的关键路径进行优化、 设置逻辑配置选项和逻辑最小化选项等。

用户还可以在编译之后, 观察划分结果, 做些必要的改动, 然后再重新编译。 这种交互式的方法可以加快开发过程。 即使对最复杂的设计也是如此。 器件划分包括芯片配置和器件设定。 通过芯片配置指定哪些逻辑块必须放在同一器件中, 通过器件设定把由芯片配置定义的逻辑块映射到指定的单个或多个器件中。

资源配置即控制布局布线, 它可以放在设计项目中的任何逻辑功能上。 然而, 这种资源配置只保持在那些在逻辑综合时不会被化简掉的逻辑上, 即硬逻辑上。 硬逻辑功能包括逻辑综合时不能去掉的SOFF、 TRI、 INPUT、 OUTPUT、 BIDIR、 LCELL和所有的触发器图元(原语)。 在宏功能块上进行的配置只保持在宏功能块内的硬逻辑上。 在宏功能块内部图元(原语)上的配置可以取代在宏功能块整体上的配置。 对于没有设置配置的逻辑部分, 编译器会自动配置。 • 为避免冲突, MAX+PLUSⅡ按优先次序处理资源与器件的配置。

优先级较高的配置总是取代优先级较低的配置。 编译器按以下优先级次序接受资源与器件的配置: • ① 顶层的TDF。 • ② 在图形、 文本和波形编译器中使用Assign菜单命令配置的配置文件。 • ③ 来自最后编译成功的适配文件( .fit, Fit File)。 如果编译器没有发现任何配置, 则自动进行逻辑布局布线。

2) 设定器件 • 器件设定可设为指定具体器件或AUTO。 若设为AUTO, MAX+PLUSⅡ编译器会按照最小规模和最快速度的原则将设计项目适配到具体器件中。 • 用户可以在顶层TDF的设计段中指定器件或者在最顶层设计文件中使用Assign / Device命令完成器件设定(参看4.2.3节的第二部分及图4.34)。 • 对不能装入单个器件的设计进行划分的最简单方法是自动划分。 只要没有作任何器件配置,编译器就对设计自动进行划分。

用户还可以设置每个器件的Security Bit(加密位)选项(参看4.2.3节的第二部分及图4.37)。 对具有Turbo Bit选项的器件, 也可以设置Turbo Bit选项。 • 3) 使用引脚锁定和芯片配置 • 通过引脚锁定和芯片配置命令把设计中的一些结点配置给一个或多个芯片的特定引脚或宏单元中。 • ① 在图形或文本设计文件中高亮选择待配置的结点。 • ② 在顶层设计文件编辑窗口或平面布局图编辑器窗口中使用菜单命令Assign / Pin/Location/Chip assignments进入引脚锁定与芯片配置对话框。

③ 参照4.2.3节第二部分中的引脚锁定部分, 在图4.38和图4.39中选择或输入相关的配置项。 • ④ 选择OK, 完成设置。

4) 使用合并(Clique) • Clique逻辑配置选项用于控制逻辑的布局与布线。 合并配置应尽可能地将所选定的逻辑放置在同一芯片中的同一行中或同一LAB中, 使LAB之间、 器件之间相联系的信号数目最少, 确保在关键的定时路径上没有不必要的LAB到LAB或器件到器件的延时, 以优化逻辑布局达到高速工作。

MAX+PLUSⅡ编译器默认用Clique设置整个逻辑。 为了进一步控制关键部分逻辑的优化布局与布线, 可以在图形 , 文本或波形编译器中使用Assign / Cliquec菜单命令送入合并配置项, 也可以在高一层的TDF的设计段中送入此项配置。 使用Clique命令送入配置的步骤如下: • ① 在设计文件或平面布局图编辑器中高亮选择一组结点、 引脚及逻辑符号。 • ② 使用菜单命令Assign / Clique, 打开Clique对话框, 如图4.94所示。

③ 在Clique Name框中键入合并名, 或从下拉式列表框中选择已有的合并名。 • ④ 选择Add即将该合并项添加到设计项目合并项列表中。 或者选择Change钮, 用选定的逻辑更改先前已定义的合并项。 • ⑤ 选择OK, 则对于图形设计文件, 该合并名出现在所选定逻辑符号左上角。

5) 更多的资源配置控制方法 • 用户可以通过使用全局逻辑器件配置来控制器件的资源占用情况。 对于FLEX器件, 可以预置I/O脚、 逻辑单元利用率、 选择配置方法、 配置器件中的多用途配置引脚以及控制器件级复位和使能引脚。 对于其它器件, 可以预置I/O、 逻辑单元利用率和设置安全(保密)位。

① 选项菜单命令Assign / Global Project Device Options, 进入图4.37所示的全局逻辑器件配置对话框。 • ② 设置保密位, 预置I/O和逻辑单元利用率。 • ③ 设置其它选项。 • ④ 选择OK, 完成设置。

3. 使用编译设置 • 所有的设计项目的逻辑综合控制、 器件划分及资源配置都存放在ACF文件中。 正常情况下, MAX+PLUSⅡ 编译器会根据ACF文件的设置来编译设计项目。 用户也可以使编译器忽视已有的ACF文件指示的设置, 而按照MAX+PLUSⅡ的默认设置来编译设计项目。 MAX+PLUSⅡ 还提供了清除ACF文件中的设置项以及用当前编译结果设置覆盖ACF文件中的相应设置项的命令。

1) 忽略编译设置 • 忽略编译设置指示编译器忽视设计项目的部分或全部器件及资源配置项, 而使用MAX+PLUSⅡ的默认设置来编译设计项目。 • 用户可以在含有器件及资源配置的项目没有适配成功的情况下使用忽略编译设置, 并重新编译该设计项目, 以确定某些设置是否影响了适配, 并调整不合理的设置。 • ① 在编辑器或编译器窗口选择菜单命令Assign / Ignore Project Assignments, 出现图 4.95 所示对话框。

② 选择要忽略的设置项, 并选择OK。 • ③ 重新编译项目。 • 2) 清除项目编译设置 • 清除项目编译设置即删除项目配置文件ACF中的部分或全部的探针、 器件及资源配置项, 而不管这些配置项是否由配置菜单命令或手工编辑过。 在清除项目编译设置后, 配置菜单对话框中的Existing Assignmentstype 栏中仅显示ACF文件中剩余的配置项。 在图形编辑器窗口, 可以使用Options / Show All命令在图中显示相应的配置项。