Micro-Controller 8051 Overview

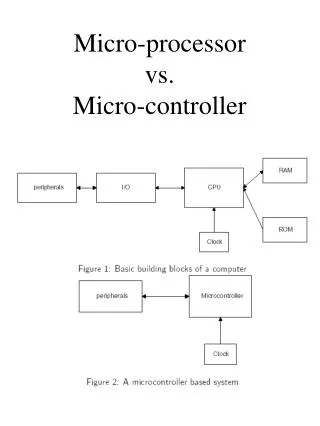

Micro-Controller 8051 Overview. MCS-51 Family Overview. 80C51 Family Products. Pin Compatible. MCS-51 Family Overview. Architectural Structure of the 8051 Family. COUNTERS. FREQUENCY REFERENCE. OSCILLATOR & TIMMING. ROM / EPROM. RAM. TWO 16-BIT TIMER/EVENT COUNTERS. CPU.

Micro-Controller 8051 Overview

E N D

Presentation Transcript

Micro-Controller 8051 Overview

MCS-51 Family Overview 80C51 Family Products • Pin Compatible MicroProcessor Part II

MCS-51 Family Overview Architectural Structure of the 8051 Family COUNTERS FREQUENCY REFERENCE OSCILLATOR & TIMMING ROM / EPROM RAM TWO 16-BIT TIMER/EVENT COUNTERS CPU 64K BYTE BUS EXPANSION CONTROL PROGRAMM- ABLE I/O • PROGRAMMABLE • SERIAL PORT • FULL DUPLEX UART • SYNCHRONOUS SHIFTER Int INTERRUPTS Ext INTERRUPTS CONTROL PARALLEL PORTS ADDRESS DATA BUS I/O PINS SERIAL IN / SERIAL OUT MicroProcessor Part II

MCS-51 Family Overview Internal Block Description MicroProcessor Part II

MCS-51 Family Overview Main Features of 8051 UART : Universal Asynchronous Receiver/Transmitter MicroProcessor Part II

MCS-51 Family Overview External Pin Description P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 Address/Data Bus Bidirection I/O Port /PSEN ALE /EA /RST P1.7 P1.6 P1.5 P1.4 P1.3 P1.2 P1.1 P1.0 Bidirection I/O Port P3.7 P3.6 P3.5 P3.4 P3.3 P3.2 P3.1 P3.0 RD WR T1 T0 INT1 INT0 TXD RXD P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0 A15 A14 A13 A12 A11 A10 A9 A8 Bidirection I/O Port Address Bus Bidirection I/O Port MicroProcessor Part II

MCS-51 Family Overview Executing From External Program Memory Timing CLK ALE /PSEN PORT2 PORT0 1 2 3 4 5 6 7 8 9 10 11 12 1 2 3 4 LATCH Bus Cycle MicroProcessor Part II

MCS-51 Family Overview Executing From External Program Memory Structure 8 0 5 1 EPROM DATA(AD7~AD0) P1 P0 /EA ALE LATCH A7~A0 Lower Addr. Addr Upper Addr. (A15~A8) P3 P2 /OE /PSEN MicroProcessor Part II

8 0 5 1 EPROM P1 P0 LATCH /EA ALE Addr P3 P2 /OE /PSEN MCS-51 Family Overview Executing From External Program Memory Example 87h Read Address 0421h (87h) Upper Address : 04h Lower Address : 21h EA : High : Internal Data Memory EA : Low : External Data Memory P0 : Address / Data I/O Port P2 : Address Bus MicroProcessor Part II

MCS-51 Family Overview Executing From External Data Memory Structure 8 0 5 1 RAM P1 P0 LATCH Addr ( 0~64KB) ALE 216 = 64KB RD WR P3 P2 /CE DECODING WR /OE MicroProcessor Part II

MCS-51 Family Overview Executing From External Data Memory Timing - Read CLK ALE PSEN /RD PORT2 PORT0 1 2 3 4 5 6 7 8 9 10 11 12 1 2 3 4 LATCH Bus Cycle MicroProcessor Part II

MCS-51 Family Overview Executing From External Data Memory Timing - Write CLK ALE PSEN /WR PORT2 PORT0 1 2 3 4 5 6 7 8 9 10 11 12 1 2 3 4 LATCH Bus Cycle MicroProcessor Part II

MCS-51 Family Overview Instruction Decoder INSTRUCTION REGISTER AND DECODER ACCUMULATOR TEMP REG FLAG ACCUMULA- TOR LATCH ARITHMETIC LOGIC UNIT CONDITION BRANCH LOGIC INT0 INT1 CARRY ACC TIMER …. … 1. Store the OP Code 2. Decoding 3. Output Control Signal DECIMAL ADJUST MicroProcessor Part II

MCS-51 Family Overview Arithmetic Logic Unit INSTRUCTION REGISTER AND DECODER ACCUMULATOR TEMP REG FLAG ACCUMULA- TOR LATCH ARITHMETIC LOGIC UNIT CONDITION BRANCH LOGIC INT0 INT1 CARRY ACC TIMER …. … Input : 1 or 2 x 8bit data Output : 8bit result data 1. +, - (carry) 2. Increment, Decrement 3. Bit Complement 4. Rotate Left/Right 5. Nibble Exchange 6. *, / DECIMAL ADJUST MicroProcessor Part II

INSTRUCTION REGISTER AND DECODER ACCUMULATOR TEMP REG FLAG ACCUMULA- TOR LATCH ARITHMETIC LOGIC UNIT CONDITION BRANCH LOGIC INT0 INT1 CARRY ACC. TIMER … .... DECIMAL ADJUST MCS-51 Family Overview Accumulator 1. Store Input Data 2. Store Result Data 3. Transfer data to Memory and I/O MicroProcessor Part II

MCS-51 Family Overview CPU Timing (I) Machine Cycle consists of six states ( 12 oscillator periods) OSC (xtal1) ALE S1 S2 S3 S4 S5 S6 S1 S2 S3 S4 S5 S6 STATE 1-BYTE, 1-CYCLE Instruction (INC a ) READ NEXT OPCODE AGAIN READ OPCODE READ NEXT OPCODE ( DISCARD) 2-BYTE, 1-CYCLE Instruction (ADD a , #data ) READ NEXT OPCODE READ OPCODE READ 2nd BYTE MicroProcessor Part II

MCS-51 Family Overview CPU Timing (II) OSC (xtal1) ALE S1 S2 S3 S4 S5 S6 S1 S2 S4 S3 S5 S6 STATE READ NEXT OPCODE AGAIN 1-BYTE, 2-CYCLE Instruction (INC DPTR ) READ OPCODE READ NEXT OPCODE ( DISCARD ) MicroProcessor Part II

MCS-51 Family Overview CPU Timing (III) OSC (xtal1) ALE S1 S2 S3 S4 S5 S6 S1 S2 S4 S3 S5 S6 STATE 1-BYTE, 2-CYCLE Instruction (MOVX) NO FETCH NO FETCH READ OPCODE READ NEXT OPCODE ( DISCARD ) ACCESS EXTERNAL MEMORY MicroProcessor Part II

MCS-51 Family Overview Memory Organization Logical Separation of Program and Data Memory PROGRAM MEMORY (READ ONLY) DATA MEMORY (READ/WRITE ONLY) FFFF FFFF Ext Ext 216 0FFF /EA=0 Ext /EA=1 Int FF Int Int 4KB =4096B Int 0000 00 / RD / WR / PSEN MicroProcessor Part II

MCS-51 Family Overview Program Memory • After reset, the CPU begins execution from location 0000h • The interrupt causes the CPU to jump to that location, where it commences execution of the service routine Ex) External Interrupt = 0003h • The lowest 4K bytes of program memory can be either in the On-chip ROM or in an External ROM( /EA (=External Access )) • The read Strobe to external ROM, /PSEN, is used for all external program fetches. /PSEN is not activate for internal program fetches. MicroProcessor Part II

MCS-51 Family Overview Program Memory Internal Program Memory :Lower 4KB region of the program memory 0FFF Longer service routines can be jump instruction PROGRAM LOCATIONS 002B If an interrupt service routine is short enough ( as is often the case in control applications), it can reside entirely within that the 8-byte interval. 0023 001B INTERRUPT LOCATIONS 0013 8 BYTE 000B 0003 RESET 0000 MicroProcessor Part II

MCS-51 Family Overview Data Memory • Internal Data Memory space is shown divided into three blocks, which are generally refereed to as the lower 128, the Upper 128, and SFR space • Internal Data Memory Address are always 1 byte wide ( 256Byte ) FF Accessible by direct Addressing PORTS STATUS BIT CONTROL BIT TIMER REGISTERS STACK POINT ACCUMULATOR (ETC..) UPPER 128 Special Function Registers 80 7F Accessible by indirect Addressing only LOWER 128 00 Accessible by direct and indirect addressing MicroProcessor Part II

MCS-51 Family Overview The Lower 128 Byte of internal RAM The Lower 128 Byte of internal RAM 3F ~ 7F STACK 20 ~ 2F BIT-ADDRESSABLE SPACE 11 18 ~ 1F BANK SELECT BIT IN PSW 10 10 ~ 17 4 BANKS OF REGISTER (R0~R7) 01 08 ~ 0F 00 00 ~ 07 MicroProcessor Part II

MCS-51 Family Overview 4 Banks Of Register 4 X 8 REGISTER BANK R7 R6 R5 R4 R3 R2 R1 R0 4th REG. BANK 3rd REG. BANK 2nd REG. BANK R7 R6 R5 R4 R3 R2 R1 R0 1st REG. BANK MicroProcessor Part II

CY AND CY Bit Address MCS-51 Family Overview Bit-Addressable Register 7F 7E 7D 7C 7B 7A 79 78 2Fh Boolean Instruction ( Bit Operation ) 77 76 75 74 73 72 71 70 2Eh AND, OR, CLEAR, SET COMPLEMENT, MOVE BIT ….. Ex) ANL CY, Bit Address ANL CY, 27h.3 Before : CY 1 (27h) 0 0 1 0 1 1 1 0 After : CY 1 0F 0E 0D 0C 0B 0A 09 08 21h 07 06 05 04 03 02 01 00 20h MicroProcessor Part II

MCS-51 Family Overview Special Function Register (SFR) - (I) 1. Software Control/Operation ( Acc, B, DPTR, PSW, SP ) 2. Internal Unit Control MicroProcessor Part II

MCS-51 Family Overview Special Function Register (SFR) - (II) MicroProcessor Part II

MCS-51 Family Overview Special Function Register (SFR) - (III) - Software Control/Operation • Acc : 8 Bit Accumulator ( Arith./Logical Operation) • B : General Purpose Register : X , / • DPTR : 16Bit Register , 8-bit accessable. ( using address pointer in the transmit External Data transfer ) • PSW : 8 Bit -Register, ( carry, Overflow, Parity Flag, Selection of the Register Bank ) • SP : Stack Point , 8-Bit Register MicroProcessor Part II

MCS-51 Family Overview Special Function Register (SFR) - (III) - Internal Unit Control • Timer/Count : TH1, TL1, TH0, TL0, TMOD, TCON • Serial Port : SBUF, SCON, PCON • Interrupt control : IE, IP • I/O Port : P0, P1, P2, P3 MicroProcessor Part II

Chap2 . The Instruction of 8051 Family Instruction Set 1. Data Transfers Instructions 2. Arithmetic Instructions 3. Logical Instructions 4. Boolean Instructions 5. Jump Instructions 5 Groups - 51 Instructions MicroProcessor Part II

Chap2 . The Instruction of 8051 Family The Concepts of OPCODE & OPERAND Instruction Code 1 Byte Instr. OP Code + Operand (Specification of the Operation) (Specification of the Address) The length of an Instruction depends on 1. The number of operands it involves 2. The Way it specifies each operands MicroProcessor Part II

Opcode Operand field 1 Operand field 2 Chap2 . The Instruction of 8051 Family Some Inst. Formats of the Intel 8085 Single-byte zero address Instruction Single-byte one address Instruction Single-byte two address Instruction Two-byte one address Instruction Three-byte one address Instruction MicroProcessor Part II

Chap2 . The Instruction of 8051 Family • Every general-purpose computer has its own unique instruction. • The Instruction Code is a group of bits that tell the computer to perform a specific operation. • Operation Code : It define such operations as add, subtract, multiply, shift, and complement. Total number of operations obtained determines the set of machine operations. Opcode must consist of at least n bits for a given 2n (or less) distinct operations. • Instruction (=Macro-Instruction) = The Sequences of Micro-Instruction MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instructions • 1. The Immediate Addressing Mode • 2. The Direct Addressing Mode • 3. The Register Addressing Mode • 4. The Register-Specific Addressing Mode • 5. The Register Indirect Addressing Mode • 6. The Register Indexed Addressing Mode MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1.Data Transfer Instruction- The Immediate Addressing Mode • The Immediate Addressing Mode : Immediate addressing, or perhaps more explicitly, immediate constant addressing, refers to the source being a constant embedded into code. Mova , #1;{ 7401h } = {Opcode+Operand} Include Data Register(Acc, SFR), Memory Org 8000h ; set the origin mov a, #0h ; put 0 into the accumulator mov a, #11h ; put 11h into the accumulator mov a, #27 ; put 27(Dec) = 1bh into the accumulator • Start Addressing : 8000h of external RAM • The sequence of Accumulator : ??h > 00h > 11h > 1bh MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instruction- The Immediate Addressing Mode Ex ) MOV A , #33h MOV DPTR , #1234h DPTR PROGRAM MEMORY PROGRAM MEMORY ACC DPH DPL 33h 12h 34h 74 90 OP CODE OP CODE 33 12 IMMEDIATE DATA IMMEDIATE DATA 34 MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instruction- The Immediate Addressing Mode Ex ) Org 8000h ; set the origin mov psw, #0 ; select register bank 0 mov r0, #0 ; put 0 into register0 mov r1, #1 ; put 1 into register1 mov psw, #8 ; select register bank 1 mov r0, #0 ; put 0 into register0 mov r1, #1 ; put 1 into register1 Org 8000h ; set the origin mov 70h, #0 ; put 0 into internal register 70 mov 71h, #1 ; put 1 into internal register 71 Org 8000h ; set the origin mov DPTR, #1234h ; place 12h into DPH and 34h DPL MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instruction- The Direct Addressing Mode • The Direct Addressing Mode : The Direct addressing mode refers to specifying an internal data register or an SFR by its address. Org 8000h ; set the origin mov a, 70h ; copy contents ofinternal register 70h to a mov a, #0 ; clear the accumulator mov 90h, a ; copy the accumulator contents to SFR 90h MOV ……. , …….. Internal Data Memory Acc, Reg .. Internal Data Memory Internal Data Memory MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instruction- The Direct Addressing Mode Ex ) mov A , 33h mov 30h , R7 DATA MEMORY DATA MEMORY ACC R7 D1 DE 33h D1 DE 30h DATA DATA < Instr. Code > mov A , #33h :74 33 mov A , 33h :E5E0 MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instruction- The Direct Addressing Mode Ex ) mov 30h , 35h mov 06h , 00h DATA MEMORY PROGRAM MEMORY DATA MEMORY PROGRAM MEMORY DATA 85 30h D1 85 00h DE 30 06 35 00 35h D1 06h DE DATA MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instruction- The Direct Addressing Mode Ex ) Port 4 equ 0E8h ; port 4 Port 1 equ 090h ; port 1 Org 8000h ; set the origin mov a, Port4; copy the contents of port 4 (= E8h) mov Port1, a; copy the acc. contents to contents of port 1 ljmp 8000h ; repeat MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instruction- The Register Addressing Mode • The Register Addressing Mode : The Register addressing mode refers to either the source or the destination being one of the eight registers of the currently selected register bank. MOV PSW, #00010000B ; BANK SELECT (BANK1) MOV A, #30h ; Immediate Addressing Mode MOV R1, A ; R1 = 30h MOV R3, #20h 1010 10110010 0000 MOV R0, R1 ; REG REG (X) MicroProcessor Part II

Chap2 . The Instruction of 8051 Family Cf ) Program Status Word (PSW) • The PSW contains several status bit that reflect the current state of the CPU. CY AC F0 RS1 RS0 OV P PSW0 PARITY OF ACCUMULATOR SET BY HARDWARE TO 1 IF IT CONTAINS AN ODD NUMBER OF 1S, OTHERWISE IT IS RESET TO 0 PSW7 CARRY FLAG RECEIVES CARRY OUT FROM BIT 1 OF ALU OPERANDS PSW6 AUXILARY CARRY FLAG RECEIVES CARRY OUT FROM BIT 1 OF ADDITION OPERANDS PSW1 USER DEFINABLE FLAG PSW2 OVERFLOW FLAG SET BY ARITHMETIC OPERATIONS PSW5 GENERAL PURPOSE STSTUS FLAG PSW4 REGISTER BANK SELECT BIT 1 PSW3 REGISTER BANK SELECT BIT 0 MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instruction- The Register-Specific Addressing Mode • The Register-Specific Addressing Mode : Some instructions are specific to the registers used. inc a ; increase contents of accumulator ; 04h inc DPTR ; increase contents of DPTR ; A3h org 8000h ; set the origin mov a, #1 ; move the contents 1 into the accumulator mov 0E0h,#1 ; move the contents 1 into SFR E0h ljmp 0 ; return to the monitor MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instruction- The Register-Specific Addressing Mode mov a, #1 ;move the contents 1 into the accumulator PROGRAM MEMORY “take the following byte and place in the accumulator” = the accumulator being the destination is implicitlycoded in the instruction 74 01 MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instruction- The Register-Specific Addressing Mode mov 0E0h, #1 ;move the contents 1 into SFR E0h PROGRAM MEMORY the following 2 bytes 75 first is the address of register E0 put the second byte to E0h ( = SFR ) 01 E0h 01 = SFR MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instruction- The Register Indirect Addressing Mode • The Register Indirect Addressing Mode • : The address of the source or destination is not given explicitly. • Instead, the contents of a register is used as the target address. org 8000h ; set the origin mov PSW, #0 ; select register 0 mov R0, #78h ; move 78h into register 0 mov @R0, #1 ; set the register whose address is specified in ; the R0 register to the constant 1 ljmp 0 ; return to the monitor MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1. Data Transfer Instruction- The Register Indirect Addressing Mode mov R0, # 40h mov A, @R0 mov R1, # 50h mov @R1, #ADh Acc DATA MEMORY DATA MEMORY 35 35 AD 40h 50h MicroProcessor Part II

Chap2 . The Instruction of 8051 Family 1.Data Transfer Instruction- The Register Indirect Addressing Mode mov @R0, 40h DATA MEMORY 55 40h 55 R1 MicroProcessor Part II

R7 R6 R5 R4 R3 R2 R1 R0 Chap2 . The Instruction of 8051 Family Addressing Mode - The Source & Destination of MOV Instruction INTERNAL DATA MEMORY mov 77h, DPL FFh 7Fh SFR mov b, a 80h 00h mov a, 88h mov 33h, R7 REGISTERs Acc mov a, 77h mov 10h, 77h mov a, R3 MicroProcessor Part II