Physikalische Basis der Angriffen

370 likes | 523 Vues

Physikalische Basis der Angriffen. Physikalische Basis der Angriffen. Algorithmische Implementierungs-Schwächen Implementierung der Algorithmen mit CMOS-Logik - Feldeffekt-Transistoren - CMOS-Gatter Angriffstechniken - Messbare Werte passive Angriffstechniken

Physikalische Basis der Angriffen

E N D

Presentation Transcript

Physikalische Basis der Angriffen • Algorithmische Implementierungs-Schwächen • Implementierung der Algorithmen mit CMOS-Logik - Feldeffekt-Transistoren - CMOS-Gatter • Angriffstechniken - Messbare Werte passive Angriffstechniken - Beinflussbare Zustände aktive Angriffstechniken • Angriffsmethoden: Klassifizierung der Angriffe nach dem Zustand des angegriffenen Gerätes • Beispiele Angriffstechniken

Kryptographie: Implementierungs-Schwächen Realer Fall: dem Angreifer sind noch mehrere Zwischenwerte bekannt Idealer Fall

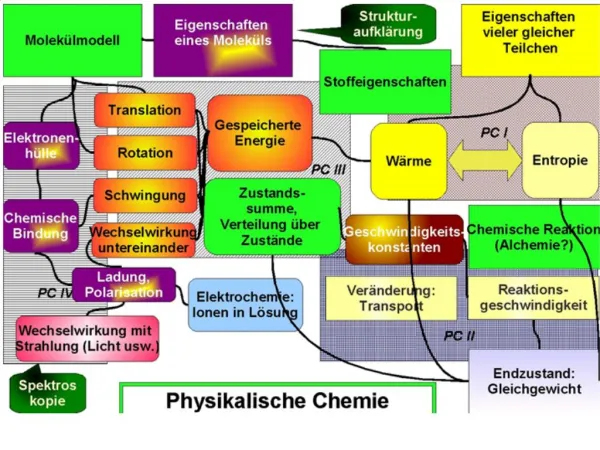

Basis für Angriffe Krypto- system √ kryptographische Funktionen (Algorithmen) encryption / decryption digitale signature generation / verification mathematische Operationen Multiplikation ; Division Addition; Subtraktion jetzt Hardware-Implementierung CMOS-Technologie: elementare Funktionen als Gatter aus Hersteller-Biblothek 4 CMOS-Logik: Vor- und Nachteile

Halbleiter http://www.filmscanner.info/CCDSensoren.html http://www.leifiphysik.de/web_ph10/grundwissen/15dotierung/dotierung.htm

Feldeffekt-Transistor MOSFET (metal–oxide–semiconductor field-effect transistors) 0 V Metall Isolator + + + + + + + + + - - - p-dotiertes-Substrat 0 V

Feldeffekt-Transistor +5 V Metall Isolator + + + + + + + + + - - - p-dotiertes-Substrat 0 V

Feldeffekt-Transistor +5 V 0 V Metall Isolator + + + + + + - - - p-dotiertes-Substrat + + + 0 V

Feldeffekt-Transistor +5 V +5 V 0 V Metall Isolator + + n-Kanal + + + n -Typ n -Typ + + + + - - - p-dotiertes-Substrat

Feldeffekt-Transistor Output Input +5 V +5 V 0 V Metall Isolator + + + + - - - - - - - - - - + n-Typ n-Typ + + + + p-Substrat +5 V . ON 0 V Output +5 V Input 0 V

Feldeffekt-Transistor Input Output +0 V +5 V 0 V Metall Isolator + + + + + n-Typ n-Typ + + + + p-Substrat +5 V . OFF +5 V Output 0 V Input 0 V

Feldeffekt-Transistor MOSFET (metal–oxide–semiconductor field-effect transistors) 0 V Metall Isolator - - - - - - - - - + + + n-dotiertes-Substrat 0 V

Feldeffekt-Transistor -5 V Metall Isolator - - - - - - - - - + + + n-dotiertes-Substrat 0 V

Feldeffekt-Transistor -5 V 0 V Metall Isolator - - - - - - + + + - - n-dotiertes-Substrat 0 V -

Feldeffekt-Transistor -5 V 0V -5 V Metall Isolator - - p-Kanal - - - p -Typ p -Typ - - - - + + + n-dotiertes-Substrat 0 V

Feldeffekt-Transistor Input Output -5 V 0V -5 V Metall Isolator - - - - ++ + + + + + + + + + + - p-Typ p-Typ - - - - n-Substrat 0V +5 V ON ON -5 V Input 0 V Input . . 0 V Output +5 V Output -5 V 0V

Feldeffekt-Transistor Input Output 0V 0V -5 V Metall Isolator - - - - - p-Typ p-Typ - - - - n-Substrat OFF OFF 0V +5 V 0 V Input +5 V Input . . -5 V Output 0 V Output 0V -5 V

Feldeffekt-Transistoren für CMOS-Logik n-Kanal-Feldeffekttransistor: nMOSFET +5 V ON OFF p-Kanal-Feldeffekttransistor:pMOSFET . . . Input +5 V +5 V +5 V +5 V +5 V +5 V OFF Output +5 V . . . 0 V ON Output 0 V 0 V 0 V +5 V +5 V Input 0 V 0 V 0 V 0 V 0 V 0 V

CMOS-Logik: Inverter Complementary metal–oxide–semiconductor +5 V +5 V ON . Input Output +5 V +5 V . . . +5 V +5 V OFF 0 V OFF ON 0 V 0 V 0 V 0 V 0 V

CMOS-Logik: Inverter +5 V +5 V OFF ON . . Input Input Output Output 0 V +5 V . . ON OFF 0 V 0 V Abbildung CMOS Logik-Gatter entnommen von: http://www.allaboutcircuits.com/vol_4/chpt_3/7.html +5 V 0 V

CMOS-Logik: NAND-Gatter Hausaufgabe: Zustand aller Transistoren für alle 4 Inputs-Kombinationen aufschreiben Abbildung CMOS Logik-Gatter entnommen von: http://www.allaboutcircuits.com/vol_4/chpt_3/7.html

CMOS-Logik: AND-Gatter Abbildung CMOS Logik-Gatter entnommen von: http://www.allaboutcircuits.com/vol_4/chpt_3/7.html

CMOS-Logik: Umschalten und Ruhezustand • neue Gatter-Inputs-Werte verursachen Umschalten der Transistoren in dem Gatter • Anzahl der umschaltenden Transistoren hängt von neuen und vorherigen Inputs-Werten ab • die Inputs-Werte sind vom „message“ und „key“ abhängig • Kenntnis der Anzahl der umschaltenden Transistoren ermöglicht das Extrahieren des Schlüssels • Zustand der Transistorenund Umschaltungsprozess sind visualisierbar!!!!

http://www.compress.ru/Article.aspx?id=22188 http://pc-inform.ru/articles/CMOS_TriGate.html In the Intel® tri-gate transistor, gates surround the silicon channel on three of four sides. Robert S. Chau, Intel

CMOS-Logik: P(T) http://people.overclockers.ru/RussOver/14701/Vysokie_toki_utechki_NVIDIA_GeForce_GTX_480_GF100

Angriffstechniken: passive und aktive • passive Angriffstechniken: Begleitende Prozesse messen und analysieren (oft Seitenkanalen-Angriffe genannt): - Waskann gemessen und analysiert werden ? - Wokann gemessen werden ? - WelcheMessgeräte ? • aktive Angriffstechniken: Zustände von Teilen des Chips beinflussen und analysieren: - Waskann beeinflusst werden ? - Wo genau ? - WelcheGeräte braucht man für Fehler-Injektionen ?

passive Angriffstechniken • Beobachtbare Prozesse bei der Umschaltung der Transistoren • Energieverbrauch (Momentanleistung messbar ) • Änderungen des elektromagnetischen Feldes (Induktionsstrom messbar) • Ausführungszeit der Algorithmen (Anzahl der Taktzyklen) • Lokale Temperatur-Änderungen sind sichtbar (zeitliche und räumliche Wärmeverteilung ist sichtbar) • Optische Emission (Lumineszenz) ist sichtbar • Beobachtbarkeit der Schaltung • Optical / infra-red / backside imaging um die Struktur des Chips zu analysieren • Weitere messbare Effekte: • Data remanence analysis • Analyse von Testvorrichtung / Scan Chains

aktive Angriffstechniken • Glitchattacks • Algorithmisch Anlegen spezieller Inputs, die zur Ausgabe eines fehlerhaften Outputs führen • Erhöhung der Taktfrequenz (nicht-invasiv) Wenn der längste Pfad der Signalverzögerung größer ist, als die Periode, kann ein Teil der Register den richtigen Inhalt nicht haben • Erhöhung der Betriebsspannung (nicht-invasiv) Beinflusst die Breite des Kanals und ändert die Zeit der Umschaltung der Transistoren; was den längsten Pfad der Signalverzögerung ändert ähnliche Wirkung wie bei der Erhöhung der Taktfrequenz • UV-Blitz-Belichtung des entpackten Chips Beinflusst mittels des Photoeffektes die leitende Eigenschaften des Kanals ähnliche Wirkung wie bei erhöhter Taktfrequenz • Elektromagnetische Impulse (auf entpacktem oder nicht entpacktem Chip) Können Strom in der Schaltung induzieren, die eine fehlerhafte Funktion des Chips verursachen

aktive Angriffstechniken • Fault injection (auf entpacktem Chip) • optical fault (UV)/ laser fault • thermal fault • lokale EM-Induktion • Hardware brute-force • Laser-scanning • Direkte Veränderungen der Struktur • Reverse-Engineering

Angriffsmethoden: Zustand des Chips • nicht-invasiv an einem funktionsfähigem, nicht entpacktem Chip • invasiv an einem entpacktem Chip, mit direktem elektrischen Kontakt; Struktur des Chips kann teilweise zerstört oder verändert werden • semi-invasiv an einem entpacktem Chip, ohne direkten elektrischen Kontakt; Struktur des Chips wird nicht zerstört oder verändert