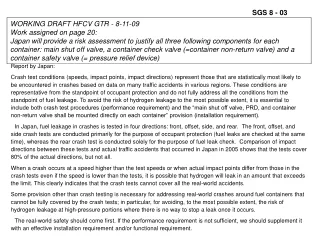

Japan Report

Japan Report. Naoaki Yamanaka. Table of contents. Japan Chapter of the IEEE Society on CPMT Report of “ 2002 IEEE SYSTEMS PACKAGING JAPAN WORKSHOP ” Call for participation of “ 2002 ICEP ” Call for papers “ The 6th VLSI Packaging Workshop of Japan ” Select paper form IEMT/IMC Japan.

Japan Report

E N D

Presentation Transcript

Japan Report Naoaki Yamanaka

Table of contents • Japan Chapter of the IEEE Society on CPMT • Report of “2002 IEEE SYSTEMS PACKAGING JAPAN WORKSHOP” • Call for participation of “2002 ICEP” • Call for papers “The 6th VLSI Packaging Workshop of Japan” • Select paper form IEMT/IMC Japan

Japan Chapter of the IEEE Society on Components, Packaging and Manufacturing Technology Society Chair Noboru Ichinose Waseda Univ. Vice Chair Naoaki Ymanaka NTT Network Innovation Labs. Vice Chair Masayoshi Umeno Chuo Univ. Secretary Nobuo Iwase Toshiba Research Consulting Co. Ltd. Treasurer Kaoru Hashimoto Fujitsu Laboratories Ltd.

Dr. Naoaki Yamanaka Biographical Sketch (M’85-SM’96-F’00) Born : July 22, 1958, Miyagi, Japan Education : Keio University, Japan where he received B.E., M.E. and Ph.D. degrees in engineering in 1981, 1983 and 1991, respectively. Job History : In 1983 he joined Nippon Telegraph and Telephone Corporation's (NTT's) Communication Switching Laboratories, Tokyo Japan, where he was engaged in research and development of a high-speed switching system and high-speed switching technologies for Broadband ISDN services. Since 1994, he has been active in the development of ATM base backbone network and system including Tb/s electrical/optical backbone switching as NTT's Distinguished Technical Member. He is now researching future optical IP network, and optical MPLS router system. He is currently a senior research engineer, supervisor, and research group leader in Network Innovation Laboratories at NTT. Honors and Awards : The Best of Conference Awards from the 40th, 44th and 48th IEEE Electronic Components and Technology Conference in 1990, 1994 and 1998. The Advanced Packaging Prize Paper Award (Best paper) of IEEE CPMT Transaction Part B in 1996. The Best Paper Awards of Microelectronics symposium in 1998 and 1999. The IEICE Best Transaction Paper Award in 1999. The Outstanding Technical Paper Award from IEEE/IMAPS the 2nd IEMT/IMC Symposium in 1998. And the 10th TELECOM System Technology Prize from the Telecommunications Advancement Foundation in 1994. Society Membership : Member at Large of IEEE CPMT, Technical Editor of IEEE Communication Magazine, Broadband Network Area Editor of IEEE Communication Surveys, Editor of IEICE Transaction, TAC Chair of Asia Pacific Board at IEEE Communications Society, an IEEE Fellow and a member of the IEICE. Present Occupation and Address : Senior Research Engineer, Supervisor, Research Group Leader NTT Network Innovation Laboratories 3-9-11 Midori-cho, Musashino-shi, Tokyo 180-8585, Japan Tel 0422-59-2047 Fax 0422-59-6387 E-mail Yamanaka.Naoaki@lab.ntt.co.jp Prof.Dr. Umeno Masayoshi Born : March 10, 1938, Nara, Japan Education : B.S. degree in Electrical Engineering from Nagoya Institute of Technology, in 1960. M.S. degree from Tokyo Institute of Technology in 1962. Dr. Eng. degree from Nagoya University in 1967. The research was supervised by Professor Tetsuya Arizumi : The study on the electron-hole plasmas in Ge and its instability Job History : Joined Nagoya University, in 1962. Up to 1978, he worked for microwave semiconductor and photon-drag IR detectors. From 1978 to 2001, he was a professor in Nagoya Institute of Technology and he was responsible for developing high efficient Solar Cells, and GaAs/Si laser. Presently, he is a professor of Chubu University, developing various Electronic and Optical Devices and its Packaging. Honors and Awards : Yonezawa award from IEICE in 1966, Academic progress award from IEE Japan in 1991, Paper Award from laser Society of Japan in 1999. Fellow from IEICE in 2001. Society Membership : IEEE member , IEICE member Chairman of Electronic Materials and Components in IEICE. General Chairman of 7th International. Photovoltaic Science Conference Engineering. International Advisory Boad in Internatinal Photovoltaic Conference. Present Occupation and Address : Professor, Electronic Engineering, Chubu University. 1200 Matsumoto-cho Kasugai 487-8501. Japan Phone +81-568-51-9244 Fax +81-568-1478 E-mail : umeno@solan.chubu.ac.jp New members

Table of contents • Japan Chapter of the IEEE Society on CPMT • Report of “2002 IEEE SYSTEMS PACKAGING JAPAN WORKSHOP” • Call for participation of “2002 ICEP” • Call for papers “The 6th VLSI Packaging Workshop of Japan” • Select paper form IEMT/IMC Japan

2002 IEEESYSTEMS PACKAGING JAPAN WORKSHOP • Date:Feb. 4 – 6 , 2002 • Site: NTT Musashino R&D Center, Tokyo • General Chair: Tohru Kishimoto (NTT) • Vice Chair: Yuzo Shimada (NEC) • Participants: 84 • Workshop Presented by: CPMT's Systems Packaging Technical Committee & The IEEE Computer Society and Computer Packaging Japan Committee

2002 IEEESYSTEMS PACKAGING JAPAN WORKSHOP • Committee Members: JAPAN Haruhiko Yamamoto (FUJITSU) Keiichiro Nakanishi (HITACHI) Kimihiro Yamanaka (IBM) Yasushi Kodama (IBM) Yutaka Tsukada (IBM) Masanobu Kohara (MITSUBISHI) Michitaka Kimura (MITSUBISHI) Yuzo Shimada (NEC) Tohru Kishimoto (NTT) Tetsuo Mikazuki (NTT) Yoshimitsu Arai (NTT) Tomotoshi Sato (ASET) Yasuhiro Yamaji (ASET) Yutaka Okabe (ASET) Toshiyasu Takei (Nagano Oki) Yuhiko Fujiwara (OKI) Yoshitaka Fukuoka (DTCT)

Committee Members: USA Robert W. Guernsey (IBM) George A. Katopis (IBM) Gordon J. Robbins (IBM) John W. Balde (IDC) Robert C. Pfahl (MOTOROLA) Iwona Turlik (MOTOROLA) Leonard W. Schaper (University of Arkansas) Committee Members: EUROPE Erich Klink (IBM) Karel Kurzweil (BULL) Adviser : Akira Masaki (OKAYAMA UNIV.) Koji Nihei (WASEDA UNIV.) Hiroshi Shibata (OSAKA INSTITUTE OF TECHNOLOGY) Tadao Ichikawa (TOSHIBA ENGINEERING) Toshihiko Watari (NEC) 2002 IEEESYSTEMS PACKAGING JAPAN WORKSHOP

2002 IEEESYSTEMS PACKAGING JAPAN WORKSHOP • Program (Monday, February 4 ) 10:30-10:40 Opening remarks 10:40-11:00 Welcome message from CPMT L. W. Schaper (Univ. of Arkansas) 11:00-12:00 Keynote Session: Packaging Technology in the Future “Packaging Technology in the Future” H. Kasuga (NEC) 12:00-13:00 Lunch • 13:00-15:30 Technical Session :High Performance Systems Packaging 13:00 System Packaging Technology of the IBM e-server Z series 900 H. Harrer (IBM) 13:30 A novel package design for high performance Unix servers E. Klink (IBM) 14:00 Daughter Board Mounting Systems for IP Network Equipment K. Saito (OKI) 14:30 Hardware Technologies for High-end Server iPX7800 K. Umezawa (NEC) 15:00 Optical Intra-Cabinet Interconnections S. Karashima (ASET) 15:30-16:00 Break • 16:00-17:30 Technical Session: Packaging Technology for High Frequency and Wireless Application 16:00 Low Cost Plastic Packaging for GHz Devices Y. Takahashi (FUJITSU) 16:30 MV (Multi Via) Technology for Wireless Applications K. Iijima (FUJITSU) 17:00 Low-cost 60GHz-band Modules for High-speed Short-range Communication Systems K. Maruhashi (NEC) 18:00-20:00 Banquet

2002 IEEESYSTEMS PACKAGING JAPAN WORKSHOP • Program (Tuesday, February 5)-am • 9:00-10:30 Technical Session: Packaging Technology for Optical Communication Systems 9:00 Chip Level Optical Packaging H. Takahara (NTT) 9:30 OEMCM Packaging Technologies N. Kosyoubu and H. Takahara (NTT) 10:00 Dual-wavelength Single-fiber Transceivers J. Matsui (JAE) 10:30-11:00 Break • 11:00-12:00 Special Session: Micro Electronics Mechanical Systems Technology for Systems Packaging 11:00 Ball Semiconductor M. Yoshida (Ball Semiconductor Ltd.) 11:30 How to industrialize the enabling technology of MEMS B. Brox (Imego AB) 12:00-13:00 Lunch

2002 IEEESYSTEMS PACKAGING JAPAN WORKSHOP • Program (Tuesday, February 5)-pm • 13:00-14:00 Technical Session :Environment, Safety and Health Technology 13:00 Best Composition for Sn-Ag-Cu lead-free Alloy K. Suganuma (Osaka Univ.) 13:30 New Flame-retarding Epoxy Resin Compounds without Halogen and their Application to Electronic Devices Y. Kiuchi, and M. Iji (NEC) 14:00-14:30 Break • 14:30-17:00 Technical Tour Telecommunication History Museum in Musashino R&D Center • 17:00-18:00 Technical Session : Packaging Technology for Personal and Mobile Information Systems 17:00 Low-impedance line Component for Power de-coupling Circuit S. Yoshida and H. Tohya (NEC) 17:30 Thermal Engineering for Systems Packaging W. Nakayama (Therm Tech International) 18:00-20:00 Banquet

2002 IEEESYSTEMS PACKAGING JAPAN WORKSHOP • Program (Wednesday, February 6 ) • 9:30-12:00 Technical Session :Latest News for Future Packaging Technology 9:30 System Architecture Implications of 3-D Interconnect Technologies L. W. Schaper and S. A. Spiesshoefer (University of Arkansas) 10:00 Multilayer Thin Film Technology for Future Microwave Systems-in-a-Package Integration W. De Raedt and E. Beyne (IMEC) 10:30-11:00 Break 11:00 Hyperfine Flip-Chip Bonding and Non-Destructive Inspection Technologies for 3D System-in-a-Package T. Fujii, Y. Tomita, T. Morifuji, T. Ando, T. Sato, and K. Takahashi (ASET) 11:30 Simultaneous Formation of Wiring and Via Using Photo-Induced Selective Plating T. Hiraoka (TOSHIBA) 12:00-13:00 Lunch • 13:00-14:30 Special Session :Electronic System Integration for Systems Packaging 13:00 Optoelectronic Micro System Integration: S-FOLM, PL-Pack with SORT, and SOLNET T. Yoshimura (Tokyo University of Technology) 13:30 Opto-electronic Hybrid Integration Technology in ASET O. Ibaragi (ASET) 14:00 Three Dimensional (3-D) LSI Chip Integration Technology in ASET K. Takahashi (ASET) 14:30 Closing (Committee meeting)

ACCESS The workshop will be held in English. All attendees are expected to be specialists in the field and to participate in discussion. We are confident that the technical meeting will be rewarding and useful. We are looking forward to a lot of participants.

Table of contents • Japan Chapter of the IEEE Society on CPMT • Report of “2002 IEEE SYSTEMS PACKAGING JAPAN WORKSHOP” • Call for participation of “2002 ICEP” • Call for papers “The 6th VLSI Packaging Workshop of Japan” • Select paper form IEMT/IMC Japan

2002 ICEP International Conference on Electronics Packaging(Formerly IEMT/IMC Symposium) April 17-19, 2002Dai-ichi Hotel Seafort Tennoz Isle, Tokyo, Japan “New Packaging Waves from Asia” Sponsored by: JIEP/ IMAPS Japan IEEE CPMT Japan Chapter

April 17 (Wed.) • WA1:High Speed / High Frequency Packaging Chairperson: R. Tummala (Georgia Institute of Technology), O. Ibaragi (ASET) • Directions in Rf Module Packaging (Session Invite), S.-K. Chiang, Prismark Partners / U.S.A. • WB1: Pb-free Solders Chairperson: M. Otsuka (Shibaura Institute of Technology), H. Sawai (Oki Electric Industry) • JIEP Low Temperature Soldering Project (Session Invite)K. Suganuma, Osaka University / Japan • Invited Speech Chairperson: S. Denda (Nagano Prefectural Institute of Technology), K.Hashimoto (Fujitsu Laboratories) • Device Packaging in the Year 2020, Dr. C. E. Bauer, TechLead Corporation / U.S.A. • Asia Session

April 18 (Thu.) • TA1: Advanced Packaging Chairperson: C. E. Bauer (TechLead), M. Tsukamoto (Matsushita Electric Industrial) • Recent Advances in Integral Passives Research at GeorgiaTech (Session Invite), R. R. Tummala, S. Bhattacharya, S. Dalmia, P. M. Raj,T. Ogawa, S. H. Lee, R. Mani, A. Bavisi, F. Ayazi,Georgia Institute of Technology / U.S.A. • The Growth of the Flip Chip Market: New Applicationsand Developments (Session Invite), E. J. Vardaman, TechSearch International / U.S.A. • TB1: Plating Chairperson: E. Zakel (Pac Tech), A. Okuno (Sanyu Rec) • TA2: Optoelectronics Chairperson: S.-K. Chiang (Prismark Partners), Y. Ando (Fujikura) • TB2: Materials Chairperson: Z. Kachwalla (CSIRO), I. Kaneko (Musashi Institute of Technology) • TA3: Interconnection I Chairperson: J. Maattanen (Elecoteq Network), H. Matsubara (Sharp) • High Speed Laser Solder Jetting Technology for Optoelectronicsand MEMS Packaging (Session Invite), E. Zakel, L. Titerle, T. Oppert, R. Blankenhorn, Pac Tech /Germany, U.S.A. • TB3:Simulation Chairperson: H. Nishida (International Display Technology) E. Takagi (Toshiba) • Study of Beyond GHz Signal Integrity Under TEM WaveMode Analysis in Multi-channel Transmission Lines(Session Invite), K. Otsuka, C. Ueda, Meisei University, Y. Odate,T. Usami, University of Tokyo / Japan

April 19 (Fri.) • FA1: 3D Packaging Chairperson: M.-K. Iyer (Institute of microelectronics), S. Uegaki (Kyocera) • FB1: Interconnection II Chairperson: Y.-B. Sun (Kyonggi University), I. Watanabe (Hitachi Chemical) • New Concepts in Flipchip Bump Technology (Session Invite), S. Denda, Nagano Prefectural Institute of Technology / Japan • FA2: Design and Testing Chairperson: S.-L. Fu (I-Shou University), S. Oka (Mitsubishi Electric) • FB2: Thermal Management Chairperson: C. Zardini (University Bordeaux I), S. Kitajo (NEC) • FA3: Substrates Chairperson: H. Quinones (Asymtek), H. Hozoji (Hitachi) • FB3: Reliability Chairperson: F. Uchikoba (TDK), T. Kobayashi (Tohoku Epson)

16th Microelectronics Show • TOTAL ELECTRONICS PACKAGING EXHIBITION • Organizer: JIEP(Japan Institute of Electronics Packaging) • Place: Tokyo Ryutsu Center (TRC) • Date : April 17 (Wed) -19 (Fri), 2002 • Hours: 10:00 - 17:00 (16:00 on the last day) • The most effective way of showing your advanced packaging technology to engineers. • The Show is held along with the largest International Conference, 2002 ICEP. • Exhibition site is at Tokyo Ryutsu Center, along Tokyo Monorail line. • Exhibitors can make free technical presentations on company's products.

General Chairperson S. Wakabayashi (Shinko Electric Industries Co., Ltd.) Vice Geneeral Chair K. Hashimoto (Fujitsu Laboratories Ltd.) S. Nishi (Konica Corporation) I. Watanabe(Hitachi Chemical Co., Ltd.) Advisory S. Denda (Nagano Prefectural Institute of Technology) K. Nihei (Waseda Univ.) Accounting S. Wakabayashi (Shinko Electric Industries Co., Ltd.) Publicity K. Tsunoi (Fujitsu Limited) Social Arrangement H. Asai (Toshiba Corporation) Publication M. Ohshima (Kogyo Chosakai Publishing Co., Ltd) Operation T. Nishikawa (OpNext Japan, Inc.) S. yamamichi (NEC Corporation) H. Hirai (D. T. Circuit Technology Co. Ltd.) M. Kikuchi (Citizen Watch Co., Ltd.) K. Kurata (NEC Corporation) S. Maeda (Konica Corporation) Technical Program K. Hashimoto I. Watanabe Y. Ando (Fujikura Ltd.) H. Hozoji (Hitachi Ltd.) O. Ibaragi (Association of Super-Advanced Electronics Technologies) I. Kaneko (Musashi Institute of Technology) S. Kitajo (NEC Corporation) T. Kobayashi (Tohoku Epson Corporation) H. Matsubara (Sharp Corporation) H. Nishida (International Display Technology) S. Oka (Mitsubishi Electric Corporation) A. Okuno (Sanyu Rec Co., Ltd.) M. Otsuka (Shibaura Institute of Technology) H. Sawai (Oki Electric Industry Co., Ltd.) E. Takagi (Toshiba Corporation) M. Tsukamoto (Matsushita Electronic Industrial Co., Ltd.) F. Uchikoba (TDK Corporation) S. Uegaki (Kyocera Corporation) S. Yoshida (Tokyo Institute, Polytechnic University) Organizing Committee

Table of contents • Japan Chapter of the IEEE Society on CPMT • Report of “2002 IEEE SYSTEMS PACKAGING JAPAN WORKSHOP” • Call for participation of “2002 ICEP” • Call for papers “The 6th VLSI Packaging Workshop of Japan” • Select paper form IEMT/IMC Japan

The 6th VLSI Packaging Workshop of Japan November 11-13, 2002Kyoto Research Park, Kyoto, Japan The VLSI Packaging Workshop of Japan held every second year since 1992 in theancientcapitalof Kyoto has become a well known international workshop of advanced packaging technologies. To monitorthelatest trend and focus on the future target, the committee strongly urges you to attend this workshop and participate in the discussion. Bring your latest research results and exchange your opinion with internationally acclaimed experts from industry and academia. Besideengineers involved with packaging, wafer processing experts and circuit designers are cordially invited to bring their breakthrough ideas to solve the current problems of SiP and SoC. Emerging technologies and latest designs in the following areas are of interest to the participants.

Program Chair : Tomoshi Ohde, Sony Semiconductor Kyushu Corp. General Chair: Atsushi Nakamura, Hitachi, Ltd. Vice Chair: Masahiko Kohno, Dow Chemical Japan George Harman, NIST Japanese committee: Kanji Otsuka, Meisei Univ. Toshio Sudo, Toshiba Nobuo Kamehara, Fujitsu Fuminori Ishitsuka, NTT Electronics Noboru Iwasaki, NTT Electronics Michitaka Kimura, Mitsubishi Tadaaki Mimura, Matsushita Yasufumi Uchida, Oki Hyung-Woo Lee, Tessera Japan Kimihiro Yamanaka, IBM Hisashi Tomimuro, NTT Electronics Hiroshi Shibata, Osaka Inst. Tech. Hisao Kasuga, NEC Kunihiko Nishi, Hitachi US committee: John W. Balde, IDC Phillip Garrou, Dow Chemical Sheng Liu, Wayne State Univ. Len Schaper, Univ. of Arkansas Ephraim Suhir, IOLON E. Jan Vardaman, TechSearch European committee: Herbert Reichl, Tech. Univ. of Berlin Asian committee: Jung-Ihl Kim, Amkor, Korea Kyung-Wook Paik, KAIST, Korea Randy Lo, ITRI/ERSO, ROC Ricky Lee, HKUST, Hong Kong C. P. Hung, ASE, Taiwan Thiam-Beng Lim, IME, Singapore IEEE CPMT Japan Chapter: Nobuo Iwase, Toshiba Hajime Sakamoto, Ibiden The 6th VLSI Packaging Workshop of Japan Committee

Selected Paper form VLSI Packaging Japan • Authors who give outstanding papers will receive official recommendations for paper submission to IEEE Transactions on CPMT by the Japan Chapter and the Workshop Committee.

Table of contents • Japan Chapter of the IEEE Society on CPMT • Report of “2002 IEEE SYSTEMS PACKAGING JAPAN WORKSHOP” • Call for participation of “2002 ICEP” • Call for papers “The 6th VLSI Packaging Workshop of Japan” • Select paper form IEMT/IMC Japan

Selected papers from IEMT/IMC Japan • It encouraged me to hear that you will contribute to handle the manuscripts which will/was send/sent to CPMT Society from CPMT Japan Chapter as recommended papers to publish at the CPMT Transactions. • The following 23 technical titles (and manuscripts) had been sent to CPMT Society as the recommended papers to publish at CPMT transactions from CPMT Japan Chapter or IENT/IMC Technical Program Committee chairs, during 1997 to 2000. Unfortunately, most of the manuscript had not been published except 3 paper. • 1997 5 • 1998 7 (including 3 which had been published on Aug. 2000 Trans.) • 1999 5 • 2000 6