Verano 2004

Organización del Computador I Verano Riegos de Control en la máquina segmentada Basado en el capítulo 6 del libro de Patterson y Hennessy. Verano 2004. Profesora Borensztejn. Dependencias de Control.

Verano 2004

E N D

Presentation Transcript

Organización del Computador I VeranoRiegos de Control en la máquina segmentadaBasado en el capítulo 6 del libro de Patterson y Hennessy Verano 2004 Profesora Borensztejn

Dependencias de Control • Definen el secuenciamiento del programa. La estructura segmentada asume secuenciamiento implícito (PC=PC+4). • La presencia de una instrucción de salto representa un riesgo para el pipeline. • Las instrucciones and, or,add y sw deben ejecutarse si la evaluación de la condición de salto es FALSE. En caso contrario, la ejecución continúa a partir de la instrucción lw (60) 40 beq $1, $3, 60 44 and $12, $2, $5 48 or $13, $6, $2 52 add $14, $2, $2 56 sw $15, 100($2) 60 lw $4,50($7)

Etapas de la instrucción de salto IR<---MEM[PC]; PC<--PC+ 4; BusA<--R[rs]; BusB<--R[rt]; dst<--- PC+4+ Signext(inm16)*4; Z<-- (BusA==BusB) ; si (Z) entonces PC<---dst; • Cálculo de la dirección efectiva: EX • Evaluación de la condición : EX • Ejecución del salto: cambio del PC: MEM

Camino de Datos con Señales de Control Salto Zero MUX 32 IF/ID ID/EX EX/MEM MEM/WB 32 + PC+4 32 4 >>2 RegW 5 W_src rs Alusrc LRA WE 5 rt LRB 5 WR 32 Registros PC @ Memoria de Instrucciones inst BusW Memoria de Datos ALUctr Inm16 Ext Control ALU rt rd Aluop RegDst

Riesgo de Control: Detener 9 1 2 3 4 5 6 7 8 ciclos El CPI de la instrucción de salto es 4 Beq $1, $3, 60 M M Reg Reg M NOP M NOP Latencia M NOP And $12, $2, $5 M M Reg Reg

Reducir latencia: anticipar operaciones M M Reg Reg Reg Reg 9 1 2 3 4 5 6 7 8 ciclos El CPI de la instrucción de salto es 3 Beq $1, $3, 60 M M Reg Reg M NOP Latencia=2 M NOP M And $12, $2, $5 Or $13, $6, $2 M

Detección del riesgo y Detener • La lógica está en ID. • Hay una instrucción en IF que hay que detener ===> poner a 0 el registro IR de IF/ID y congelar el PC. • Ecuaciones del Control de Riesgos: • Si (IF/ID.IR.cod==Salto ) PCWrite=0 ; IF.Flush=1 • Si (ID/EX.MEM.Salto=1 ) PCWrite=0 ; IF.Flush=1 • Si (EX/MEM.MEM.Salto=1 ) PCWrite=0 ; IF.Flush=1

Detección y Detención PCsrc ID/EX EX/MEM Salto Riesgos de Control Salto IF/ID PCWrite IF.Flush Z IF/ID.IR.codop nop ID/EX.Salto EX/MEM.Salto

Mejora: Suponer Salto no Realizado 1 2 3 4 5 6 7 8 ciclos Suponemos que el salto no se realiza Si es correcto, CPI del salto es 1. Si es incorrecto, hay que eliminar las instrucciones que están en el pipeline. CPI=4 Beq $1, $3, 60 M M Reg Reg M And $12, $2, $5 Reg M Reg Eliminar !! M M Or $13, $6, $2 Reg Reg M M Add $14, $2, $2 Reg Reg lw $4,50($7) M M Reg Reg

Mejora: Suponer Salto no Realizado 1 2 3 4 5 6 7 8 ciclos Beq $1, $3, 60 M M Reg Reg M And $12, $2, $5 Reg Eliminadas !! M Or $13, $6, $2 Reg M Add $14, $2, $2 lw $4,50($7) M M Reg Reg

Detección del error y cancelar • La lógica está en ID. • Hay una instrucción en IF, otra en ID, y otra en EX que hay que cancelar ===> señales IFFlush, IDFlush y EXFlush. • Ecuaciones del Control para el Salto: • Si (EX/MEM.MEM.Salto=1 ) y (EX/MEM.Z=1) IF.Flush=1; ID.Flush=1; EX.Flush=1;

Detección y Cancelar PCsrc PCWrite ID/EX Unidad de Riesgos EX/MEM ID.Flush MUX 0 EXFlush Unidad de Control MUX Salto IF/ID MUX 0 IF.Flush 0 IR Z MUX EX/MEM.Z nop EX/MEM.Salto

Salto Retardado • Aproximación basada en el compilador • Redefine el comportamiento del salto: se ejecuta después de la siguiente instrucción. • El compilador debe insertar instrucciones después de la instrucción de salto que siempre se ejecutarán. • Cuantas? Dependiendo de la latencia del salto, la arquitectura define cuantos “branchdelay slots”debe rellenar el compilador.

Instrucción de Salto Retardado 36 sub $10, $4, $8 40 beq $1, $3, 64 44 and $12, $2, $5 48 or $13, $6, $2 52 add $14, $2, $2 56 sw $15, 100($2) 60 j 90 64 lw $4,50($7) 36 beqd $1, $3, 64 40 sub $10, $4, $8 44 and $12, $2, $5 48 or $13, $6, $2 52 add $14, $2, $2 56 sw $15, 100($2) 60 j 90 64 lw $4,50($7)

Salto Retardado 1 2 3 4 5 6 7 8 ciclos Beqd $1, $3, 60 La instrucción que sigue al salto siempre se ejecuta La latencia del salto es 2. M M Reg Reg sub $10, $4, $8 M Reg M Reg NOP Latencia 2!! NOP lw $4,50($7) M M Reg Reg

Salto Retardado: Elección de la instrucción • Instrucción del Bloque Básico al que pertenece la instrucción de salto • Instrucción de uno de los dos posibles Bloques Básicos que se ejecutará. sub $10, $4, $8 Beqd $1, $3, 60 And $12, $2, $5 or $13, $6, $2 add $14, $2, $2 sw $15, 100($2) lw $4,50($7) j 90 lw $4,50($7)

add $10, $4, $8 Beqd $1, $3, 60 Salto Retardado: Elección de la instrucción • Instrucción del Bloque Básico al que pertenece la instrucción de salto Beqd $1, $3, 60 add $10, $4, $8 • La instrucción elegida no debe ser fuente de dependencia con la instrucción que evalúa la condición.

Salto Retardado: Elección de la instrucción • Instrucción perteneciente al Bloque Básico que se ejecuta si se cumple la condición. #1 : add $10, $4, $8 sub $2, $7, $8 Beq $1, $3, #1 #1: sub $2, $7, $8 Beqd $1, $3, #1 add $10, $4, $8 • La instrucción elegida no debe afectar el estado si no se salta. add $10, $4, $8 #1: sub $2, $7, $8 Beqd $1, $3, #1 add $10, $4, $8 add $4, $10,$7 add $10, $4, $8 #1: sub $2, $7, $8 Beqd $1, $3, #1 add $10, $4, $8 add $10, $5,$7

Beq $1, $3, #1 Beqd $1, $3, #1 And $12, $2, $5 or $13, $6, $2 add $14, $2, $2 #1: Beqd $1, $3, #1 Beqd $1, $3, #1 And $12, $2, $5 or $13, $6, $2 add $14, $2, $2 #1: And $12, $2, $5 or $13, $6, $2 add $14, $2, $2 #1: Sub $6, $7, $12 And $12, $2, $5 or $13, $6, $2 add $14, $2, $2 #1: Sub $12, $2, $5 Salto Retardado: Elección de la instrucción • Instrucción perteneciente al Bloque Básico que se ejecuta si no se cumple la condición. • La instrucción elegida no debe afectar el estado si se salta.

Evaluación de las alternativas de salto Esquema Penalización CPI medio Mejora respecto a detener Detener 3 Suponer No Efectivo 3 Salto Retardado 2

Salto Retardado • Introducido en 1952! MANIAC I • Usado en microprogramación • Reinventado en la RISC-I (Patterson y Sequin, 1981) • MIPS (1982), RISC-II(1983), MIPS-R desde 1987 hasta ahora ) y AMD 29000 (1987) • Compiladores llenan el 60 % de los slots con instrucciones útiles. • Ventajas: cerca de un 10% de mejora • Desventajas: • aumento en el código: en algunos casos hay que replicar instrucciones, se insertan NOP’s. • problemas con las interrupciones: salvar múltiples PC’s • problemas cuando el procesador se vuelve superescalar:

Saltos Incondicionales IR<---MEM[PC]; PC<--PC+ 4; dst<--- (inm26)*4; PC<---dst; • Cálculo de la dirección efectiva: D • Ejecución del salto: cambio del PC: D

Salto Incondicional 1 2 3 4 5 6 7 8 ciclos Un ciclo de latencia J 60 M M Reg Reg M nop M M 60: lw $4,50($7) Reg Reg M M Add $14, $2, $2 Reg Reg sw $6,50($7) M M Reg Reg

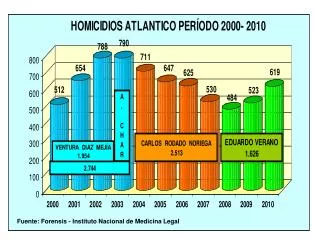

Estadísticas Distancia entre Saltos % de Saltos eqntott 2.86 35% espresso 4.81 20.8% li 6.06 16.5% Media 4.57 21.9% doduc 10.59 9.4% matrix 3000 5.05 19.8% nasa 7 10.72 9.3% spice 2g6 3.27 30.6% tomcatv 16.28 6.0% Media 9.18 10.9%