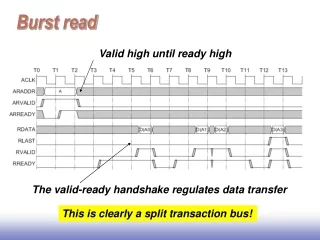

Burst read

This guide explains the intricacies of burst read and write transactions in the AXI protocol, highlighting ordering restrictions and data transfer regulations. Learn about the handshake process, overlapping bursts, and how transactions from different masters interact. Explore the rules for read and write transactions, as well as the specifics of the AHB-APB bridge and state diagram.

Burst read

E N D

Presentation Transcript

Burstread Valid high until ready high The valid-ready handshake regulates data transfer This is clearly a split transaction bus!

Overlapping burst read Address of second burst issued: True outstanding transactions

Orderingrestrictions AXI Transactions from different masters have NO ordering restrictions. They can complete in any order. M1 S1 M2 S2 Transactions from the same master, but with different ID values, have NO ordering restrictions. They can complete in any order. AXI M1 S1 ID=8 ID=5 ID=8 ID=5 M2 S2 AXI WRITE TRANSACTIONS Write transactions from the same master AND the same AWID must complete in the same order the master issued the addresses in. M1 S1 ID=5 ID=5 ID=5 ID=5 M2 S2

Orderingrestrictions READ TRANSACTIONS Read transactions with the sameARID: AXI Read data should return in the same order that the addresses are received by the slave. M1 S1 ID=5 ID=5 ID=5 ID=5 M2 S2 AXI M1 S1 Read data should return in the same order that the master issued the addresses in. ID=5 ID=5 M2 S2 ID=5 Read and write transactions from the same master and with same AWID=ARID have no ordering restrictions. What if ordering is actually needed in this case?

Simple rules A simple master can issue transactions with the same ID (implicitely forcing in-order delivery) A simple slave can serve requests in the order they arrive, regardless of the ID tag

AHB-APB bridge CLKH These are all AHB signals High-performance Low-power (and performance) CLKL

State Diagram The APB should be used to interface to any peripherals which are low-bandwidth or do not require the high performance of a pipelined bus interface When AHB (the only master on the APB) wants to drive a transfer One cycle penalty for APB peripheral address decoding Transfer happens here NOTE: no multi-cycle (burst) transfers, no pipelining

Writecycle on the APB Control signals must be kept stable Control signals may glitch De-asserted unless a new transfer to the same peripheral has to take place Setup Enable Idle

Readcycle Sampling at the end of the enable cycle

ReadCycle AHB-APB Data forwarded asynchrounously or stored at the bridge Bridge Bridge can Drive HREADY to stall the transfer Read data can be Provided only during the ENABLE cycle

Burstreads on the APB • Note address latching throughout the transfer time

Writecycle AHB-APB No wait states required Bridge samples AHB data and control wires and frees the bus.

Burst writes • Wait states needed for AHB bus writes • The bridge must have 2 address registers