Efficient Verilog Coding Styles for Digital Hardware Design: Case Study of Decoders

100 likes | 129 Vues

learn various efficient Verilog coding styles for digital hardware design, including case statement, boolean expressions, and ROM implementation, optimizing implementation, readability, and reusability.

Efficient Verilog Coding Styles for Digital Hardware Design: Case Study of Decoders

E N D

Presentation Transcript

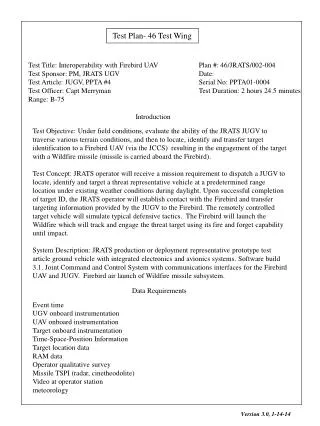

Introduction to Digital Hardware Design S04: Coding Style and Synthesis Results Dr. Khaled Benkrid (Author) k.benkrid@ieee.org Reviewed and updated by; Prof. W. Adi

Coding Style • There are many ways in which you can capture a functional specification (behaviour) in Verilog • Many aspects should be taken into account in choosing a particular coding style including: • Efficiency of the resulting implementation • Ease of coding • Readability • Reusability • Maintainability

Decoder Example OUT[0] OUT[1] OUT[2] IN[0] OUT[3] IN[1] OUT[4] OUT[5] IN[2] OUT[6] OUT[7] • Consider a 3-to-8 decoder with the following truth table:

Decoder Example – 1/3 • Using Case Statement: module Decoder_1( input [2:0] IN, output reg [7:0] OUT ); always@(IN) begin case(IN) 3'h0 : OUT[7:0] <= 8'b00000001; 3'h1 : OUT[7:0] <= 8'b00000010; 3'h2 : OUT[7:0] <= 8'b00000100; 3'h3 : OUT[7:0] <= 8’b00001000; 3'h4 : OUT[7:0] <= 8'b00010000; 3'h5 : OUT[7:0] <= 8'b00100000; 3'h6 : OUT[7:0] <= 8'b01000000; 3'h7 : OUT[7:0] <= 8'b10000000; default: OUT[7:0] <= 7'b0000000; endcase end endmodule

Decoder Example – 2/3 • Using Boolean Expressions: module Decoder_2( input [2:0] IN, output [7:0] OUT ); assign OUT[0]= ~IN[2] & ~IN[1] & ~IN[0]; assign OUT[1]= ~IN[2] & ~IN[1] & IN[0]; assign OUT[2]= ~IN[2] & IN[1] & ~IN[0]; assign OUT[3]= ~IN[2] & IN[1] & IN[0]; assign OUT[4]= IN[2] & ~IN[1] & ~IN[0]; assign OUT[5]= IN[2] & ~IN[1] & IN[0]; assign OUT[6]= IN[2] & IN[1] & ~IN[0]; assign OUT[7]= IN[2] & IN[1] & IN[0]; endmodule

Decoder Example – 3/3 • Using ROM 00000001 00000010 00000100 00001000 00010000 00100000 01000000 10000000 module Decoder_3( input [2:0] IN, output reg [7:0] OUT ); reg [7:0] Decoded[7:0] ; initial $readmemb("Mem.dat", Decoded); always@(IN) begin OUT <= Decoded[IN]; end endmodule Content of "Mem.dat”

Coding Style • Choose the simplest coding style especially if it results in the same quality of implementation • This improves programmers’ productivity and hence reduces project costs drastically in practice • Synthesis tools are getting increasingly sophisticated so simpler coding styles (i.e. more abstract) are increasingly favoured in HDL

Lab Session 4 The fourth lab session (“DecodingTheWorld” module) will create more elaborate combinational circuits using Verilog HDL. In particular, you will use more Boolean syntactical expressions and the “case” statement in Verilog to implement a 7-segment display decoder in different ways.