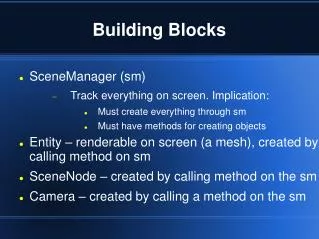

Basic Building Blocks

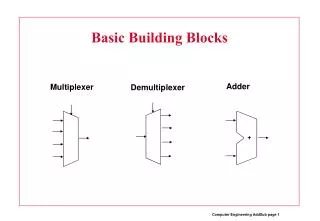

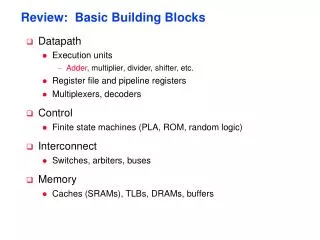

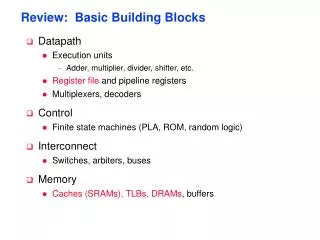

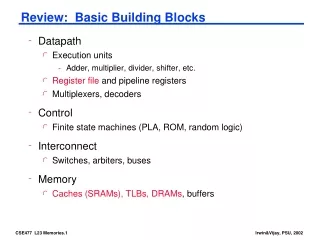

+. Basic Building Blocks. Adder. Multiplexer. Demultiplexer. The Program Counter. There is a special register inside the processor. Big enough to hold an instruction address (32 bits) . Called the program counter (PC). Zero ext. Branch logic. 0. A. ALU. 4. B. +. 31. +.

Basic Building Blocks

E N D

Presentation Transcript

+ Basic Building Blocks Adder Multiplexer Demultiplexer

The Program Counter • There is a special register inside the processor. • Big enough to hold an instruction address (32 bits). • Called the program counter (PC).

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend

Fetch - Execute • Fetch: • Send the value in the PC to the instruction memory. • The instruction memory gives out one instruction. • Execute: • Carry out the fetched instruction. • Also: PC := PC+4; Fetch Execute 108 times per second

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend

The Register File • 32 word (32 bit) registers. • r0 is special: • Read: always zero. • Write: allowed, but won´t change it. • r31 is special: • Hard-wired return address (lab1).

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend

Add Instructions • 32 bit operands. • Example: • Add rd rs rt. • rd := rs + rt. • There is also: • Addurd rs rt. • These are not add signed and add unsigned. The “u”-variant ignores overflow. 6 5 5 5 Opcode rs rt rd

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend Add rdrsrt

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend Add rd rs rt

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend Add rd rs rt

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend Add rd rs rt

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend Add rd rs rt

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend Add rd rs rt … next instr

Sub Instructions • 32 bit operands. • Example: • Subrd rs rt • rd := rs - rt • There is also: • Suburd rs rt • These are notsub signed and sub unsigned The “u”-variant ignores overflow

How to Negate • Y := -X? • Sub rd $0 rt ($0 means r0) • rd := 0 - rt • Careful: Neg Not

Compare Instructions • Signed integers: • Sltrd rs rt • if rs < rt then rd := 1else rd := 0 • Unsigned integers: • Sltu rd rs rt • if rs < rt then rd := 1else rd := 0

Immediate Variants of the arithmetic instructions: • Addi rt rs Imm • Addiu rt rs Imm • Slti rt rs Imm • Sltiu rt rs Imm • Imm sign-extend • No sub instruction

Sign/Zero extension • The immediate field is 16 bits • But most operations work on 32 bits! Zero extension Sign extension Immediate 0000000000000000 Immediate xxxxxxxxxxxxxxxx x Immediate 31 16 15 0 31 16 15 0 Bit 15, the Sign bit, is copied into bits 16 - 31

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend Addi rt rs Imm

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend Addi rt rs Imm

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend Addi rt rs Imm

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend Addi rt rs Imm

Zeroext. Branch logic 0 A ALU 4 B + 31 + Sgn/Ze extend Addi rt rs Imm … next instr