Very Simple CPU

210 likes | 252 Vues

Very Simple CPU. Speaker: Tsung-Yi Wu. Source. Source http://www.tu-harburg.de/~setb0209/cpu/. Introduction. A minimal 8Bit CPU in a 32 Macrocell CLPD. VHDL RTL code 4 instructions Simulator Assembler. Instruction Set. List. Instruction Set. Example of Program. Architecture.

Very Simple CPU

E N D

Presentation Transcript

Very Simple CPU Speaker: Tsung-Yi Wu

Source • Source • http://www.tu-harburg.de/~setb0209/cpu/

Introduction • A minimal 8Bit CPU in a 32 Macrocell CLPD. • VHDL RTL code • 4 instructions • Simulator • Assembler

Instruction Set • List

Instruction Set • Example of Program

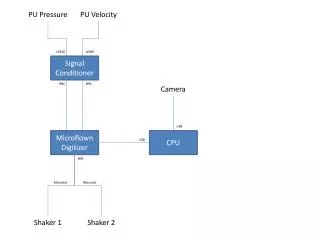

Architecture • Data Path

Architecture • FSM

RTL Code • CPU8BIT2 module CPU8BIT2 (data, adress, oe, we, rst, clk); inout[7:0] data; wire[7:0] data; output[5:0] adress; wire[5:0] adress; output oe; output we; input rst; input clk; reg[8:0] akku; reg[5:0] adreg; reg[5:0] pc; reg[2:0] states;

RTL Code • CPU8BIT2 always @(posedge clk or negedge rst) begin if (rst == 1'b0) begin adreg <= {6{1'b0}} ; states <= 3'b000 ; akku <= {9{1'b0}} ; pc <= {6{1'b0}} ; end else begin if (states == 3'b000) begin pc <= adreg + 1 ; adreg <= data[5:0] ; /* Lable1: For JCC with carry=0*/ end else begin adreg <= pc ; /* Lable1: For other case */ end

RTL Code • CPU8BIT2 case (states) 3'b010 : /* ADD */ begin akku <= ({1'b0, akku[7:0]}) + ({1'b0, data}) ; end 3'b011 : /* NOR */ begin akku[7:0] <= ~(akku[7:0] | data) ; end 3'b101 : /* JCC */ begin akku[8] <= 1'b0 ; end default : /* instr. fetch, jcc taken (000), sta (001) */ begin end endcase

RTL Code • CPU8BIT2 if (states != 3'b000) begin states <= 3'b000 ; end else if (data[7:6] == 2'b11 & (akku[8]) == 1'b1) begin states <= 3'b101 ; end else begin states <= {1'b0, ~data[7:6]} ; end end end assign adress = adreg ; assign data = (states != 3'b001) ? 8'bZZZZZZZZ : akku[7:0] ; assign oe = (clk == 1'b1 | states == 3'b001 | rst == 1'b0 | states == 3'b101) ? 1'b1 : 1'b0 ; assign we = (clk == 1'b1 | states != 3'b001 | rst == 1'b0) ? 1'b1 : 1'b0 ; endmodule

RTL Code • cpu2system module cpu2system (clk, reset); input clk; input reset; wire ncs; wire cs; wire noe; wire oe; wire we; wire[7:0] data; wire[15:0] adrram; wire[5:0] adrcpu; CPU8BIT2 CPU (.rst(reset), .clk(clk), .oe(oe), .we(we), .data(data), .adress(adrcpu)); sram16x8 RAM (.reset(reset),.data(data), .addr(adrram), .we(we), .oe(noe)); assign noe=~oe; assign adrram = {10'b0000000000, adrcpu} ; endmodule

cpu2system • Sram16x8 module sram16x8 (reset,data, addr, we, oe); input reset; input we; input oe; inout[7:0] data; input[15:0] addr; reg[7:0] mem[15:0]; /*16 bytes*/ reg[7:0] output_data; wire[3:0] short_addr; assign short_addr=addr[3:0]; assign data = (we) ? output_data : 8'bzzzzzzzz ;

cpu2system • Sram16x8 always @(reset or we or addr or oe) if (reset == 1'b0) begin /* program */ mem[0]=8'b00000100; mem[1]=8'b01000101; mem[2]=8'b11000010; mem[3]=8'b11000011; mem[4]=8'b00000000; mem[5]=8'b00000001; end else begin if (we==0) mem[short_addr]=data; else if (we==1) output_data=mem[short_addr]; end endmodule

RTL Code • Testbench module testbench (); reg clk; reg reset; cpu2system SYS (.clk(clk), .reset(reset)); always begin clk <= 1'b0 ; reset <= 1'b1 ; #50; clk <= 1'b0 ; reset <= 1'b0 ; #50; clk <= 1'b1 ; #25; reset <= 1'b1 ; #25; forever begin clk <= 1'b0 ; #50; clk <= 1'b1 ; #50; end end endmodule

Assembler • mal.exe - Assembler. • Example: (1) enter smal gcd.asm (1.1) smal will generate gcd.l and gcd.o • cpu3emu.exe - emulator • Example: (1) enter cpu3emu gcd.o (1.1) cpu3emu can emulate the execution of gcd.o

Lab • Score (65~75) • Write assembly program • A subtract B • Show result by emulator • Show result by simulator

Lab • Score (85~95) • Write assembly program • Compare A and B • A>B mem[4’b1111]=8’b00000000 • B>=A mem[4’b1111]=8’b11111111 • Show result by simulator • Show result by emulator

Lab • Final project instead of final exam. • Implement the CPU by Starter Kit • Write assembly program • Compare A and B • A>B mem[4’b1111]=8’b00000000 • B>=A mem[4’b1111]=8’b11111111 • Show result by simulator • Show result by emulator • Show result by LED • Show the big one (score 80~90) • Show memory contents (score 90~100)

Appendix • Four-Digit, Seven-Segment LED Display

Appendix • Controlling Way