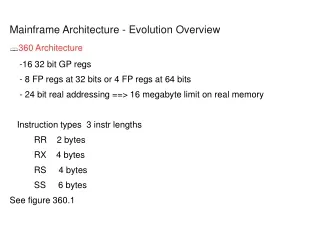

Mainframe Architecture - Evolution Overview

Mainframe Architecture - Evolution Overview. 360 Architecture -16 32 bit GP regs - 8 FP regs at 32 bits or 4 FP regs at 64 bits - 24 bit real addressing ==> 16 megabyte limit on real memory Instruction types 3 instr lengths RR 2 bytes RX 4 bytes

Mainframe Architecture - Evolution Overview

E N D

Presentation Transcript

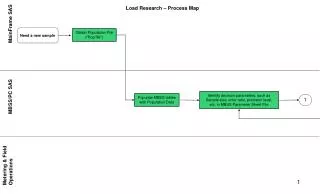

Mainframe Architecture - Evolution Overview • 360 Architecture -16 32 bit GP regs - 8 FP regs at 32 bits or 4 FP regs at 64 bits - 24 bit real addressing ==> 16 megabyte limit on real memory Instruction types 3 instr lengths RR 2 bytes RX 4 bytes RS 4 bytes SS 6 bytes See figure 360.1

Mainframe Architecture - Evolution Overview - 2 CPU modes kernel (Sup state) user (Appl state, Problem state) - Program Status Word (PSW) 8 Bytes contain mode and address of “current” instruction Mask for interrupts Condition code for Conditional branch - PSW Swap on interrupts Fixed location in low memory – depend on Interrupt type - 16 Protect keys, Reference and Change (Dirty) bits /page

Mainframe Architecture - Evolution Overview • 370 Adds virtual addressing see fig 370. Segment and page tables--- describe overview Later- Expand page table real page by 2 bits to support more real memory 16 meg * 4K = 64 meg real but still 16 meg virtual - multiple 16 meg virtual address spaces

Mainframe Architecture - Evolution Overview- 370 370 Adds virtual addressing see fig 370. Segment and page tables--- describe overview Later add page table real page # by 2 bits to support more real memory 16 meg * 4 = 64 meg real still 16 meg virtual but multiple 16 meg virt address spaces I

Mainframe Overview 370 -Adds multiprocessor support But low memory cannot be shared (interrupts, PSW swap etc) Add Prefix REG s.t. each processor has it’s own page 0 for interrupt (remember this for understanding of PR/SM later) Real Address + Prefix Reg (for page 0) === Absolute addressI

Mainframe Overview -370 370 • -Adds Dual-address-space facility -Primary and secondary virtual address spaces - Both virtual addresses use same translation technique but are used against separate sets of segment and page table CR 1 and CR 7 are 2 control regs that point to segment tables Bit in PSW designates which address space is in use Instructions are in Primary Space, Operands can be in either space (PSW bit) Address Space Number (ASN) used to designate address space New Instructions added to handle these changes

Mainframe Overview -370 -Problem: Not enough real or virtual addressing…. Enter 31 it addressing 370 and XA (Extended addressing)----.>31 bit Virtual and real 31bit address is 128 times larger that 24 bit…(lasts 5 years) Bit in PSW defines 24 bit (The Line) or 31 bit mode Some compatibility problems: e.g. BAL puts CC in high order 2 bits ===> BASM e.g. LA clears high order byte… used by some software (especially in data structures) BASM (Branch and Set Mode) also uses 32nd bit to control addressing mode (24 or 31 bit) .

Mainframe Overview - 370 Conversion to 31 bit easier than 32 bits… and eventually 64 bit Requires Segment table entry enlarged to 11 bits Requires Page table entry enlarged to 32 bits Implication of 24 and 31 bit addressing A 24 bit “line” … some applications only execute below this line (Dusty deck ) Mixed software – 24bit to 31bit, back to 24bit e.g. appl to lib(24bit stub) to real lib(31 bit) and return

Mainframe Overview 370 -> ESA -ESA/370 Addressing again Access Registers to expand data access Add 16 access registers each 32 bits One to one paired to GPR Access reg selects an address space entry (contains a STOR) See fig 370.2 ESA/390 almost no addressing change from ESA 370

Mainframe Overview Z Architecture a 64 bit architecture 64 bit General Purpose Registers (GPRs) 64 bit Control registers 64 bit real addressing 64 bit virtual addressing