DSL

DSL. Domain Specific Language (Lenguaje Especifico del Dominio). Definicion :. Es un lenguaje de programación diseñado para dar solución a unas tareas especificas. Diferente a lenguajes de propósito general como C o Java. Diseñados para resolver problemas difíciles y muy comunes.

DSL

E N D

Presentation Transcript

DSL Domain Specific Language (Lenguaje Especifico del Dominio)

Definicion: • Es un lenguaje de programación diseñado para dar solución a unas tareas especificas. • Diferente a lenguajes de propósito general como C o Java. • Diseñados para resolver problemas difíciles y muy comunes.

Otros Nombres: También son conocidos como: • Little Languages • Application Languages • Very High Level Languages

DSL Aunque parezca algo nuevo los DSL surgieron hace mucho (Cobol,Fortran…) Los DSL se han ido formando con el tiempo ha medida que se han ido haciendo necesarios.

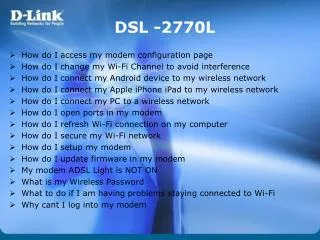

Ventajas: • Aumento de la productividad .Son mas precisos con lo que se trabaja mas rápido. • Solución expresada en el idioma y el nivel de abstracción del dominio, con lo que los expertos pueden entender, validar y modificar los programas. • Los programas son auto-documentados y pueden ser reutilizados. • Pueden ser usados por gente que no son programadores.

Desventajas: • Funcionamiento pobre ya que los lenguajes de alto nivel pueden ser ineficientes. • Gastos de producción pueden ser elevados. • Gastos de educación de los usuarios. • Duración del desarrollo muy largo(2 a 5 años) • A veces es difícil o imposible eliminar errores • Perdida de eficacia vs software codificado a mano.

EJEMPLOS:SQL • Lenguaje de acceso a base de datos relaciónales. • Aúna álgebra y calculo relacional para lanzar consultas con fin de recuperar información. • Sencillo de usar y de aprender.

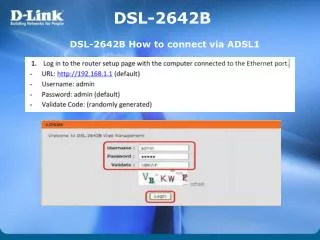

SQL:Lenguaje • CREATE: crea un objeto en la base de datos (tabla , vista, trigger…) CREATE TABLE TABLA_NOMBRE ( my_field1 INT UNSIGNED, my_field2 VARCHAR (50), my_field3 DATE NOT NULL, PRIMARY KEY (my_field1, my_field2) )

SQL:Lenguaje • ALTER: Modifica la estructura de un objeto (agregar columna a una tabla): ALTER TABLE TABLA_NOMBRE ( ADD NUEVO_CAMPO INT UNSIGNED )

SQL:Lenguaje • DROP: Elimina un objeto de la base de datos. DROP TABLE TABLA_NOMBRE ALTER TABLE TABLA_NOMBRE ( DROP COLUMN CAMPO_NOMBRE1 )

SQL:Programas • Algunos programas basados en SQL son : DB2, Oracle, SQL Server, Sybase ASE, MySQL, PostgreSQL, Firebird...

EJEMPLOS:MAPLE • Maple es un lenguaje de programación capaz de realizar cálculos simbólicos, algebraicos y de álgebra computacional.

EJEMPLO:VHDL • Lenguaje para diseñar circuitos digitales • VHDL es el acrónimo que representa la combinación de VHSIC y HDL, donde VHSIC es el acrónimo de Very High Speed Integrated Circuit y HDL es a su vez el acrónimo de Hardware Description Language.

VHDL:Lenguaje Puede usarse de tres maneras: • Funcional: como se comporta el circuito • Estructural: por componentes • Mixta: combiando las 2 anteriores

library ieee; use ieee.std_logic_1164.all; entity rfc is port( clk_i : IN std_logic; -- control inputs reset_i : IN std_logic; enable_w_i : IN std_logic; enable_r1_i : IN std_logic; enable_r0_i : IN std_logic; din_w_i : IN std_logic; dout_r1_o : OUT std_logic; dout_r0_o : OUT std_logic ); end rfc; architecture funcional of rfc is signal d:std_logic; begin process (clk_i,reset_i) begin if reset_i = '1' then d <= '0'; elsif clk_i'event and (clk_i = '1') then if enable_w_i = '1' then d<= din_w_i; end if; end if; end process; process (enable_r0_i,enable_r1_i,d) begin if enable_r0_i = '1' then dout_r0_o <= d; else dout_r0_o <= 'Z'; end if; if enable_r1_i = '1' then dout_r1_o<= d; else dout_r1_o <= 'Z'; end if; end process; end funcional; VHDL:Lenguaje RFC:funcional

library ieee; use ieee.std_logic_1164.all; ENTITY Register8 IS generic (retardo: time := 1 ns); port( clk_i : IN std_logic; -- control inputs reset_i : IN std_logic; enable_w_i : IN std_logic; enable_r1_i : IN std_logic; enable_r0_i : IN std_logic; din_w_i : IN std_logic_vector (7 DOWNTO 0); dout_r1_o : OUT std_logic_vector (7 DOWNTO 0); -- data outputs dout_r0_o : OUT std_logic_vector (7 DOWNTO 0) ); END Register8 ; architecture estructura of Register8 is component rfc port( clk_i : IN std_logic; -- control inputs reset_i : IN std_logic; enable_w_i : IN std_logic; enable_r1_i : IN std_logic; enable_r0_i : IN std_logic; din_w_i : IN std_logic; dout_r1_o : OUT std_logic; -- data outputs dout_r0_o : OUT std_logic ); end component; begin rfcs: for i in 0 to 7 generate puertas: rfc port map (clk_i,reset_i ,enable_w_i ,enable_r1_i ,enable_r0_i ,din_w_i(i) ,dout_r1_o(i) ,dout_r0_o(i)); end generate; end estructura VHDL:Lenguaje REGISTRO 8 BITS

VHDL:Lenguaje • Un ejemplo de programa que usa VHDL es ModelSim

OTROS DSL’s • HTML: HyperText Markup Language (lenguaje de marcas hipertextuales). • Open GL (graficos 3D). • Csound(crear, editar, analizar y componermúsica y sonido )basado en C.