第 6 章 输入 / 输出

第 6 章 输入 / 输出. 40. 1. A 7. IOR. IOW. A 6. 39. 2. 38. 3. A 5. A 4. 37. 4. 36. Note1. 5. EOP. READY. A 3. 35. 6. A 2. 34. HLDA. 7. MEMR. MEMW. A 1. 33. 8. ADSTB. AEN. 32. 9. A 0. HRQ. V cc. 31. 10. CS. 8237. 30. 11. DB 0. CLK. 29. 12. DB 1. 28.

第 6 章 输入 / 输出

E N D

Presentation Transcript

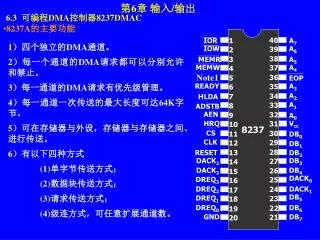

第6章 输入/输出 40 1 A7 IOR IOW A6 39 2 38 3 A5 A4 37 4 36 Note1 5 EOP READY A3 35 6 A2 34 HLDA 7 MEMR MEMW A1 33 8 ADSTB AEN 32 9 A0 HRQ Vcc 31 10 CS 8237 30 11 DB0 CLK 29 12 DB1 28 RESET 13 DB2 DACK2 DB3 27 14 DACK3 DB4 26 15 DREQ3 25 16 DREQ2 24 17 DB5 DREQ1 23 18 DREQ0 DB6 22 19 GND DB7 21 20 6.3 可编程DMA控制器8237DMAC • 8237A的主要功能 1)四个独立的DMA通道。 2)每一个通道的DMA请求都可以分别允许和禁止。 3)每一通道的DMA请求有优先级管理。 4)每一通道一次传送的最大长度可达64K字节。 5)可在存储器与外设,存储器与存储器之间、进行传送。 6)有以下四种方式 (1)单字节传送方式; (2)数据块传送方式; (3)请求传送方式; (4)级连方式,可任意扩展通道数。 DACK0 DACK1

第6章 输入/输出 A1~A4 A0~A3 IOR IOW 8086 CPU CS 8237 译码 DB0~DB7 D0~A7 IOWC IORC CLK CLK CS: 片选信号,输入,低电平有效。由高位地址码(A4—A15)译码得到对8237的片选信号。主控状态时,被自动禁止为无效。 IOR: 为输入线,CPU向8237发出的读命令。 IOW: 为输入线,CPU向8237发出的写命令,通道写入控制字或通道数据。 6.3 可编程DMA控制器8237DMAC • 8237与CPU的接口 从控制器件:8237是8086的一个外围接口 DB0~DB7: 数据输入缓冲,接受CPU的命令。 A0~A3: 输入的地址,寻址内部寄存器 CLK: 时钟输入,确定8237的工作速率

第6章 输入/输出 6.3 可编程DMA控制器8237DMAC • 8237的DMA接口 主控制器件: DB0~DB7: 输出A8~A16高位地址,(由ADSTB选通进行锁存)存贮器到存贮器传送的数据缓冲器。 A0~A3: 输出低4位地址A0~A3 A4~A7: DMA周期中通过这四条经输出的是16位存贮器地址的A4~A7位。 ADSTB: 地址选通信号,输出,高电平有效。 经DB0~DB7将高8位地址锁存在外部锁存器中。后经锁存器输出到地址总线的高8位(A8~A15) AEN: 地址充许输出信号,高电平有效。使锁存器中锁存的高8位地址送到地址总线。使CPU的地址锁存器无效,封锁CPU总线的控制。

第6章 输入/输出 IOR IOW 为输出线,8237向外部设备发出的读命令,可读取外部设备中的数据。 为输出线,8237向外部设备发出的写命令,可向外部设备写入数据。 当 有效时, 必然有效。 读写存储器控制信号,三态输出,低电平有效。 当 有效时, 必然有效。 存贮器向外部设备传送数据 MEMW MEMW IOR: 外部设备向存贮器的传送数据 MEMR MEMR: IOW: 6.3 可编程DMA控制器8237DMAC • 8237的DMA接口 主控制器件:

第6章 输入/输出 CS: 当8237处于主控状态时,被自动禁止为无效。 EOP: DMA过程结束8237复位。低电平有效,双向。 输入:低电平强迫8237结束DMA操作。 输出:低电平作为DMA传送结束的标志。 6.3 可编程DMA控制器8237DMAC • 8237的DMA接口 主控制器件: READY: 准备好信号,输入,高电平有效。若存贮器或外部设备来不及完成读/写操 作,可使READY无效,8237产生一个等待周期,直到READY有效为止。 RESET: 复位信号,输入,高电平有效。清除所有寄存器的内容,控制线浮空,禁 止DMA操作,复位后,必须重新初始化。

第6章 输入/输出 6.3 可编程DMA控制器8237DMAC • 优先级编码和循环优先级逻辑 HRQ(Hold Reguest) 总线请求信号,向CPU输出,高电平有效。当任一通道收到外部设备的 DMA请求时,8237立即向CPU发出HRQ,表示要求使用总线。 HLDA(Hold Acknowledge) 总线响应信号,由CPU输入到8237,高电平有效。 DREQ0~DREQ3 DMA请求线,编程决定输入电平的极性。必须保到DACK应答为止。 请求传送方式下必须保持到DMA传送结束。 DACK0~DACK3 DMA响应线(应答信号线)由编程决定输入电平的极性。当CPU发出总线充许信号(如HLDA)后,输出到外设表示DMA操作开始。

第6章 输入/输出 8086 CPU AB 地址 锁存 及控 制逻 辑 DB CB 地址锁存及控制逻辑 主 存 I/O0 I/O3 …… MEMR IOR ADSTB READY AEN MEMW IOW CLK CLK HOLD HRQ HLDA HLDA 8237DMAC ………… DREQ3 DACK3 DREQ0 DACK0 6.3 可编程DMA控制器8237DMAC • 8237的DMA接口

第6章 输入/输出 三种基本操作:DMA读、DMA写、DMA校验 DMA读: =0、 =0完成存贮器到I/O的传送。 DMA写: =0、 =0完成I/O到存贮器传送。 校验:伪操作,用于校验8237的内部功能,并不产生任何具体的DMA读、写操作。 • 8237DMA传送类型 IOW IOR MEMW MEMR 6.3 可编程DMA控制器8237DMAC • 8237DMA操作时序 SI:空闲周期,当8237处于无效状态时,由多个SI组成,直到HRQ有效。 S0:8237DMA的首个周期,HRQ有效后产生,连续的S0周期直到HLDA有效。 S1、S2、S3、S4:有效周期。 S1、表示进入DMA传送 正常时序: S2产生16位有效地址。 S3、S4完成数据读写操作。 压缩时序: S2产生16位有效地址。 S4完成数据读写操作。 SW:等待周期。当READY=0时在S3、S4之间插入。

第6章 输入/输出 6.3 可编程DMA控制器8237DMAC • 四种特殊传送操作 存贮器到存贮器: 只适用通道0为源,通道1目的之间的从存贮器的一块到另一块的快速数据传送。要用8个有效状态,4个有效状态通道0读、4个有效状态通道1写。 自运预置传送: 基地址、基字计数寄存器的内容自动装入当前地址、当前字计数寄存器中从而进入下一次的DMA操作。无需CPU进行预置。 循环优先: 四个通道处于平等状态,进行循环优先级管理。 压缩时序: 正常时序由三个S2、S3、S4完成数据传送而在压缩时序下只有S2、S4二个时序就可以完成数据传送。

第6章 输入/输出 HOLD HRQ 命令 REG. 8 数据.Temp.8 计数 Temp. 16 IOR READY 状态 REG. 8 地址暂存器 16 HLDA HLDA MEMR CLOCK IOW REQ MASK 方式 REG.6 请求 屏蔽 MEMW 关闭CPU地址 FLAG FLAG 通道0 AEN 基地址 REG. 16 当前地址..REG. 16 RESET 非读 可读 DREQ0 EN# ADSTB 基字节数REG.16 当前字节计数器.16 DACK0 STB DB7 : DB0 DATA SUB DREQ1 锁存器 通道1 DACK1 IO / M CS# DREQ2 地 址 总 线 ADDR. 译 码 通道2 A15~A8 DACK2 A7~A0 DREQ3 通道3 A3~A0 DACK3 EOP A7~A4 6.3 可编程DMA控制器8237DMAC • 8237的内部寄存器结构 四通道共用: (1)命令寄存器 (2)状态寄存器 (3)字计数暂存器 (4)地址暂存器 (5)数据暂存器

第6章 输入/输出 0:禁止通道0地址保存 1:允许通道0地址保存 X:当D0=0时可任意 D7 D6 D5 D4 D3 D2 D1 D0 0:正常时序 0:固定优先级 0:启动8237工作 0:DACK信号低电平有效 0:禁止存储器到存储器传送 0:DREQ信号高电平有效 1:压缩时序 X:当D0=1时可任意 1: DREQ信号低电平有效 1:循环优先级 1:存储器到存储器传送 1:停止8237工作 1: DACK信号高电平有效 0:滞后写入选择 1:扩展写入选择 X:当D0=0时可任意 6.3 可编程DMA控制器8237DMAC • 8237的内部寄存器结构 四通道共用: (1)命令寄存器(8位) 存放操作方式,CPU预置操作命令。

第6章 输入/输出 D7 D6 D5 D4 D3 D2 D1 D0 6.3 可编程DMA控制器8237DMAC • 8237的内部寄存器结构 四通道共用: (2)状态寄存器(8位) 存放各通道是否终止(=0)和请求(DREQ=1)是否有效的状态。 1:通道0终止计数 1:通道1终止计数 1:通道2终止计数 1:通道3终止计数 1:通道0请求有效 1:通道1请求有效 1:通道2请求有效 1:通道3请求有效

第6章 输入/输出 6.3 可编程DMA控制器8237DMAC • 8237的内部寄存器结构 四通道共用: (3)字计数暂存器 暂存每次DMA操作需要传送的数据字节总数值。 (4)地址暂存器(16位) 操作时完成当前地址寄存器和当前计数寄存器内容的修改。CPU不能访问。 (5)数据暂存器 (8位) 用于存放存储器到存储器传送方式中,暂时存放从源地址存储器读出的数据。

第6章 输入/输出 HOLD HRQ 命令 REG. 8 数据.Temp.8 计数 Temp. 16 IOR READY 状态 REG. 8 地址暂存器 16 HLDA HLDA MEMR CLOCK IOW REQ MASK 方式 REG.6 请求 屏蔽 MEMW 关闭CPU地址 FLAG FLAG 通道0 AEN 基地址 REG. 16 当前地址..REG. 16 RESET 非读 可读 DREQ0 EN# ADSTB 基字节数REG.16 当前字节计数器.16 DACK0 STB DB7 : DB0 DATA SUB DREQ1 锁存器 通道1 DACK1 IO / M CS# DREQ2 地 址 总 线 ADDR. 译 码 通道2 A15~A8 DACK2 A7~A0 DREQ3 通道3 A3~A0 DACK3 EOP A7~A4 6.3 可编程DMA控制器8237DMAC • 8237的内部寄存器结构 各通道专用: (1)基址寄存器 (2)当前地址寄存器 (3)基字计数寄存器 (4)当前字计数寄存器 (5)方式寄存器 (6)请求寄存器 (7)屏蔽寄存器

第6章 输入/输出 (4)当前字计数寄存器 表示操作过程中还需要传送的数据字节数。每传送一个字节,其内容减1, 直到该寄存器的内容由OOOOH减为FFFFH时,产生终止计数信号,使 变为低电平。 EOP 6.3 可编程DMA控制器8237DMAC • 8237的内部寄存器结构 各通道专用: (1)基址寄存器 保存DMA传送的起始地址值。初始化编程由CPU来预置16位地址值。不 能读出。在自动预置方式下,在有效时,自动装入当前地址寄存器。 (2)当前地址寄存器 保存DMA传送时存储单元的地址值或者存储器的当前地址值。每传送一个 字节的数据,其内容自动加1或减1。初值是基地址寄存器的内容,由CPU 同时写人,共用一个I/0地址。在编程状态下,CPU可以分二次读/写该 寄存器的内容。在自动预置方式下,在有效时,将基地址寄存器的内容自 动装入。 (3)基字计数寄存器 存放每次DMA操作需要传送的数据字节总数值, CPU预置,不能读出。

第6章 输入/输出 D7 D6 D5 D4 D3 D2 D1 D0 方式选择 通道选择 自动预置功能选择 地址增减选择 传送类型选择 0:禁止 1:允许 00:校验,空操作 01:写传送,I/O到M 10:读传送,M到/IO 11:无效 00:通道0 01:通道1 10:通道2 11:通道3 00:请求方式 01:单字节方式 10:数据块方式 11:级联方式 0:递增 1:递减 6.3 可编程DMA控制器8237DMAC • 8237的内部寄存器结构 各通道专用: (5)方式寄存器 保存DMA的传送方式和传送类型。CPU设置。

第6章 输入/输出 D7 D6 D5 D4 D3 D2 D1 D0 无定义 通道选择 请求触发器置位/复位 0:复位 1:置位 00:通道0 01:通道1 10:通道2 11:通道3 6.3 可编程DMA控制器8237DMAC • 8237的内部寄存器结构 各通道专用: (6)请求寄存器 产生软件控制下产生DMA请求,代替硬件DREQ信号,每个通道1位。只有在数据块传送下使用,在存储器到存储器的传送必须用软件请求启动通道0。

第6章 输入/输出 D7 D6 D5 D4 D3 D2 D1 D0 无定义 通道屏蔽 屏蔽 0:清屏蔽 1:置屏蔽 通道0 通道1 通道2 通道3 6.3 可编程DMA控制器8237DMAC • 8237的内部寄存器结构 各通道专用: (7)屏蔽寄存器 软件控制每个通道的DMA请求是否有效,每个通道1位。 屏蔽触发器置位,禁止该通道的DMA请求。

第6章 输入/输出 6.3 可编程DMA控制器8237DMAC • 8237编程步骤 1. 输出主清除命令 命令不需要通过数据总线写入控制字,而是通过8237A直接对地址和控制信号译码,来执行各自的功能。主清除命令该命令与硬件的RESET信号有相同的功能,它使控制、状态、请求、暂存等寄存器以及内部先/后触发器清零,使8237A进入空闲周期,以便进行编程。 2. 写入基与现地址寄存器 3. 写入基与现字节寄存器 4. 写入模式寄存器 5. 写入屏蔽寄存器 6. 写入控制寄存器 7. 写入请求寄存器

第6章 输入/输出 D7 D6 D5 D4 D3 D2 D1 D0 自动预置功能选择 传送类型选择 方式选择 地址增减选择 通道选择 00:请求方式 01:单字节方式 10:数据块方式 11:级联方式 00:通道0 01:通道1 10:通道2 11:通道3 00:校验传 01:写传送 10:读传送 11:无效 0:禁止 1:允许 0:递增 1:递减 6.3 可编程DMA控制器8237DMAC • 8237编程步骤 例, 通道0由外设写入32K字节块,传送内存起始地址8000H,增量传送,块传送。非自动初始化,外设DREQ和DACK高电有效。 方式字:10 0 0 01 00 数据块,地址增量,非自动初始化,写传送,通道0

第6章 输入/输出 D7 D6 D5 D4 D3 D2 D1 D0 通道屏蔽 屏蔽 0:清屏蔽 1:置屏蔽 通道0 通道1 通道2 通道3 6.3 可编程DMA控制器8237DMAC • 8237编程步骤 例, 屏蔽字: 0000 0000 无定义

第6章 输入/输出 D7 D6 D5 D4 D3 D2 D1 D0 0:固定优先级 0:DACK信号低电平有效 0:允许芯片工作 0:DREQ信号高电平有效 0:禁止存储器到存储器传送 1: DREQ信号低电平有效 1:禁止芯片工作 1:循环优先级 1:允许存储器到存储器传送 1: DACK信号高电平有效 6.3 可编程DMA控制器8237DMAC • 8237编程步骤 例, 命令字: 1 0 1 0 0 0 0 0 DACK高电平 DREQ高电平 扩展写 固定优先权 正常时序 允许工作 D0=0任意 非存贮器到存贮器 0:禁止通道0地址保存 1:允许通道0地址保存 X:当D0=0时可任意 0:正常时序 1:压缩时序 X:当D0=1时可任意 0:滞后写入选择 1:扩展写入选择 X:当D0=0时可任意

第6章 输入/输出 6.3 可编程DMA控制器8237DMAC • 8237编程步骤 例, 设8237片选有效的高位地址为05H而低4位由A0~A3决定(P252表6-3) OUT 5DH,AL ;主清命令 MOV AL,00H OUT 50H,AL ;写基与现地址低8位 MOV AL,80H OUT 50H,AL ;写基与现地址高8位 MOV AL,00H OUT 51H,AL ;写基与现字节计数低8位 MOV AL,80H OUT 51H,AL ;写基与现字节计数高8位 MOV AL,84H ;方式字 OUT 5BH,AL MOV AL,00H ;屏蔽字 OUT 5AH,AL MOV AL,0A0H ;命令字 OUT 58H,AL 幻灯片 24

第6章 输入/输出 0 0 CS 0 0 0 0 0 0 0 0 0 0 0 0 0 通道号 1 1 0 1 0 0 1 1 0 0 通道号 1 0 1 1 0 0 0 1 0 0 通道号 0 0 1 1 0 0 0 0 1 1 0 1 0 1 0 A3 A2 A1 A0 IOR IOW 1 0 0 1 1 0 0 通道号 0 1 0 1 1 0 1 0 1 1 1 0 1 1 0 1 1 1 0 1 0 1 1 1 1 1 0 1 0 1 1 1 0 写请求寄存器 写全屏蔽寄存器位 写命令寄存器 写单个屏蔽寄存器 读当前地址寄存器 写方式寄存器 写入地址寄存器 读数据暂存器 清除先/后触发器 读状态寄存器 读当前计数寄存器 主复位 清屏蔽寄存器 写入计数寄存器 操作对象 6.3 可编程DMA控制器8237DMAC • 8237编程步骤 返回

课后作业: • P260 • 6.8(2秒钟延时可不考虑其时间准确性) • 6.9