The COMPAAN Tool Chain : Converting Matlab into Process Networks

20 likes | 225 Vues

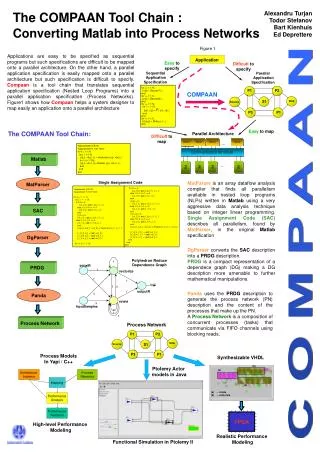

Architecture Instance. Process Networks. Parallel Architecture. FPGA. Mapping. Mem. Mem. Mem. Mem. Communication Structure. Performance Analysis. PE. PE. PE. PE. Performance Numbers. Application. %parameter N 8 16; %parameter K 100 1000; for k = 1 : 1 : K,

The COMPAAN Tool Chain : Converting Matlab into Process Networks

E N D

Presentation Transcript

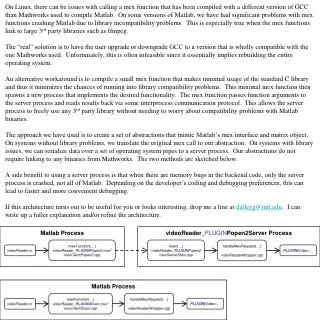

Architecture Instance Process Networks Parallel Architecture FPGA Mapping Mem Mem Mem Mem ... Communication Structure Performance Analysis PE PE PE PE ... Performance Numbers Application %parameter N 8 16; %parameter K 100 1000; for k = 1 : 1 : K, for j = 1 : 1 : N, if k-2>= 0, [ in_0 ] = ipd( r_2( k-1, j ) ); else %% if -k+1 >= 0 [ in_0 ] = ipd( r_1( j, j ) ); end if j-2>= 0, [ in_1 ] = ipd( x_3( k, j-1, j ) ); else %% if -j+1 >= 0 [ in_1 ] = ipd( x_1( k, j ) ); end [ out_0, out_1, out_2 ] = Vectorize( in_0, in_1 ); [ r_2( k, j) ] = opd( out_0 ); [ x_2( k, j) ] = opd( out_1 ); [ t_1( k, j) ] = opd( out_2 ); for i = j+1 : 1 : N, %parameter N 8 16; %parameter K 100 1000; for k = 1:1:K, for j = 1:1:N, [r(j,j), x(k,j), t ] = Vectorize( r(j,j), x(k,j) ); for i = j+1:1:N, [r(j,i), x(k,i), t] = Rotate( r(j,i), x(k,i), t ); end end end for j = 1:1:N, [x(j)] = Source1( ); end for i = 1:1:K, [y(i)] = Source2( ); end for j = 1:1:N, for i = 1:1:K, [y(i), x(j)] = F( y(i), x(j) ); end end for i = 1:1:K, [Out(i)] = Sink( y( I ) ); end Matlab if k-2>= 0, [ in_0 ] = ipd( r_3( k-1, j, i ) ); else %% if -k+1 >= 0 [ in_0 ] = ipd( r_1( j, i ) ); end if j-2>= 0, [ in_1 ] = ipd( x_3( k, j-1, i ) ); else %% if -j+1 >= 0 [ in_1 ] = ipd( x_1( k, i ) ); end if -j+i-2>= 0, [ in_2 ] = ipd( t_2( k, j, i-1 ) ); else %% if j-i+1 >= 0 [ in_2 ] = ipd( t_1( k, j ) ); end [ out_0, out_1, out_2 ] = Rotate( in_0, in_1, in_2 ); [ r_3( k, j, i) ] = opd( out_0 ); [ x_3( k, j, i) ] = opd( out_1 ); [ t_2( k, j, i) ] = opd( out_2 ); end end end MatParser MatParser is an array dataflow analysis compiler that finds all parallelism available in nested loop programs (NLPs) written in Matlab using a very aggressive data analysis technique based on integer linear programming. Single Assignment Code (SAC) describes all parallelism, found by MatParser, in the original Matlab specification SAC DgParser DgParser converts the SAC description into a PRDG description. PRDG is a compact representation of a dependece graph (DG) making a DG description more amenable to further mathematical manipulations. PRDG r initialR r vectorize r r rout t x r outputR x rotate x inputSamples Pandauses the PRDG description to generate the process network (PN) description and the content of the processes that make up the PN. A Process Network is a composition of concurrent processes (tasks) that communicate via FIFO channels using blocking reads. x r t Sink The COMPAAN Tool Chain : Converting Matlab into Process Networks Alexandru Turjan Todor Stefanov Bart Kienhuis Ed Deprettere Figure 1 Applications are easy to be specified as sequential programs but such specifications are difficult to be mapped onto a parallel architecture. On the other hand, a parallel application specification is easily mapped onto a parallel architecture but such specification is difficult to specify. Compaanis a tool chain that translates sequential application specification (Nested Loop Programs) into a parallel application specification (Process Networks). Figure1 shows how Compaan helps a system designer to map easily an application onto a parallel architecture Easy to specify Difficult to specify Sequential Application Specification Parallel Application Specification P1 P2 COMPAAN S1 Sink Source P3 P1 Easy to map The COMPAAN Tool Chain: Difficult to map Single Assignment Code COMPAAN Polyhedron Reduce Dependence Graph Panda Process Network Process Network P1 P2 S1 Source P3 P1 Process Models In Yapi / C++ Synthesizable VHDL Ptolemy Actor models in Java High-level Performance Modeling Realistic Performance Modeling Functional Simulation in Ptolemy II