Hardware/software Interfacing

Hardware/software Interfacing. Interrupt handling and using internal timer. Two way for processor to accept external input: Waiting for input: Processor will be halting and listening to the input port until data is transmitted while(data is not updated){

Hardware/software Interfacing

E N D

Presentation Transcript

Interrupt handling and using internal timer • Two way for processor to accept external input: • Waiting for input: Processor will be halting and listening to the input port until data is transmitted while(data is not updated){ read data from address of some I/O port }

Interrupt handling and using internal timer • Interrupt: Data arrival will start an interrupt request to processor, when a interrupt is generated, processor will stop it’s current work and turn to interrupt service function (data receive), and resume work after interrupt is handled. interrupt_func() { transmit data from I/O port to processor } Main() { setup interrupt handling function }

Interrupt Request • “interrupt request" (or IRQ) is used to refer to either the act of interrupting the bus lines used to signal an interrupt, or the interrupt input lines on a Programmable Interrupt Controller • Generated when an I/O event occurs, handled by interrupt controller • Interrupts from different sources are differentiated by IRQ line number

Interrupt handler function • NIOS Processer keeps a special address in memory ad the entry point for interrupt handler function • Exception Vector: stores the address of interrupt handler function, when an IRQ is received by processor, it will save the instruction context and jump to interrupt handler function.

How to use interrupt handler • Enable corresponding IRQ line to processor in SOPC builder • Set I/O devices to enable external interrupt generation Enable the interruptmask register of Parallel I/O The ITO bit in internal timer control register • Write interrupt handler function • Register interrupt handler function

Code sample for interrupt handler setup • Include files: #include "system.h" #include "alt_types.h" #include "sys/alt_irq.h" #include "sys/alt_sys_init.h"

Pseudo-Code sample for interrupt handler setup void interrupt_handler() { … } main() { enable system irq register handler of irqX as interrupt_handler }

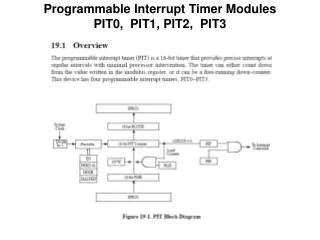

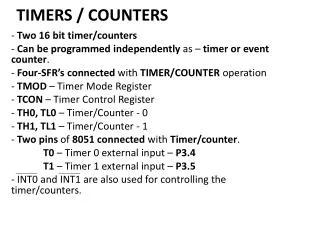

Internal Timer • NIOS Internal Timer • Works as a stop watch, period register and control signals are set by user by programming, once started, counter will count down from the value in period register to 0 and generate an interrupt when time is over.

Timer configuration Configured in SOPC Builder

How to use internal timer in programming • Internal timer will loopingly count down from value in period register to 0, when counter reaches 0, an interrupt on IRQ 1 will be generated, user need to write IRS function for IRQ 1 to capture timer events • In DE2 Computer, the period of timer is 1 ms, means the interrupt will occur 1000 per second

How to use internal timer in programming • #include "system.h" • #include "alt_types.h" • #include "altera_avalon_timer_regs.h" • #include "altera_avalon_timer.h" • #include "sys/alt_irq.h" • #include "sys/alt_sys_init.h"

Macros for timer register file access • IORD_ALTERA_AVALON_TIMER_STATUS(base) • IOWR_ALTERA_AVALON_TIMER_STATUS(base, data) // Read/write to 16 bits status register • IORD_ALTERA_AVALON_TIMER_CONTROL(base) • IOWR_ALTERA_AVALON_TIMER_CONTROL(base, data) // Read/write to 16 bits control register • IORD_ALTERA_AVALON_TIMER_PERIODL(base) • IOWR_ALTERA_AVALON_TIMER_PERIODL(base, data) // Read/write to lower 16 bits of period register • IORD_ALTERA_AVALON_TIMER_PERIODH(base) • IOWR_ALTERA_AVALON_TIMER_PERIODH(base, data) // Read/write to higher 16 bits of period register

How to use internal timer in programming • Write user IRS function static void Timer_Interrupts(void *context,alt_u32 id) { if(Timer_counter >= 1000) /* 1S */ { Timer_counter = 0; //global variable to store reached counter event <USER CODE HERE> } else { Timer_counter++; } IOWR_ALTERA_AVALON_TIMER_STATUS(TIMER_BASE, 0x00);//clear status register }

How to use internal timer in programming • Register IRS alt_irq_register(TIMER_IRQ,NULL,Timer_Interrupts); //Register IRS IOWR_ALTERA_AVALON_TIMER_CONTROL(TIMER_BASE, 0x07); //Start timer

How to capture Timer event in user program • Keep a global variable for storing information from timer events, in main function, check the global variable to update timer events static int timer_event; interrupt_handler() { …. //set timer_event } main() { register IRS function while(timer_event updated) { … user actions } }

Summary • DE2 Computer A basic hardware configuration in Quartus for embedded system software design • Parallel I/O Basic, register file structure and programming • 7-Segment LED Driven by parallel I/O, programming and display • Interrupt handling Basic concepts, and how to use in programming • Internal Timer Basic, register file structure and programming

HW 1 Answer keys 1: Draw and describe the memory hierarchy of an embedded system Figure 5-1

2 Which memory component in a memory hierarchy is typically located on board A: Level-2 cache B: Main memory C: Secondary memory D: All of the above E: None of the above D

[a] What is ROM [b] Name and describe three type of ROM ROM=Read Only Memory, a type of non-volatile memory that can be used to store data on an embedded system permanently MASK ROM OTPROM EPROM ...

[a] What is RAM [b] Name and describe 3 types of RAM Random Access Memory=location within it can be accessed directly and randomly SRAM SDRAM DRDRAM …

[a] Draw examples of ROM, SRAM and DRAM memory cells [b] Describe the main differences between these memory cells figure 5-6, figure 5-9, and figure 5-11 a ROM: contains bipolar or MOSFET transistor SRAM: 6 transistors, lost data when power off DRAM: one transistor and one capacitor, need refreshed to keep data

SRAM is usually used in external cache, because SRAM is slower than DRAM FALSE

[a] What is the difference between level1,2,3 cache • [b] How do they all work together in a system speed: fast, medium, slow cost: high, medium, low Processor first check level 1 cache, if miss, check level 2 cache … if all caches miss, goes to main memory

[a] What is the most common schemes used to store and retrieve data in cache • [b] what is the difference between cache hit and cache miss • Direct mapped, set associative, full associative • Cache hit: the data is in the cache • miss: data is not in cache

Name and describe at least 4 cache swapping schemes • Optimal, LRU, FIFO, NRU

Auxiliary memory is typically classified according to how data is accessed • True

What is the differences between physical memory and logical memory • Physical memory is the real memory on board • Logical memory is a virtual memory space, implemented by OS, to provide a convenient way for software development

17 (2) How can memory impact the performance of a system • Difference in band width and frequency can slow down data access period • Limited memory will frequently cause page fault, exchanging pages out from and into memory will be a large overhead for system.