2.6 Mikrocontroller-Beispiele

2.6 Mikrocontroller-Beispiele. 2.6.1 ATmega128 - ein kompakter Mikrocontroller. 8-Bit-Mikrocontroller Mitglied der AVR8-Familie ATmega Reihe größere Bauform als ATtiny ATtiny: DIL8, ATmega: QIL64, etwas erweiterter Prozessorkern. 2.6 Mikrocontroller-Beispiele.

2.6 Mikrocontroller-Beispiele

E N D

Presentation Transcript

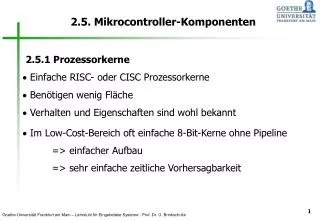

2.6 Mikrocontroller-Beispiele 2.6.1 ATmega128 - ein kompakter Mikrocontroller • 8-Bit-Mikrocontroller • Mitglied der AVR8-Familie • ATmega Reihe • größere Bauform als ATtiny ATtiny: DIL8, ATmega: QIL64, etwas erweiterter Prozessorkern

2.6 Mikrocontroller-Beispiele Einordnung in die Familie

2.6 Mikrocontroller-Beispiele • Prozessorkern • RISC-Architektur • Taktfrequenz bis 16 MHz • Harvard-Architektur mit 8 Bit Datenbus, 16 Bit Befehlsbus und 16 Bit Adressbus • 32 allgemeine 8 Bit Register, 6 davon paarweise als 16 Bit Indexregister nutzbar • 7 Adressierungsarten • Gemeinsame Adressierung (Memory Mapped IO) • 8 x 8 Bit Multiplikation • Speicher • statisches RAM • FlashRAM • EEPROM

2.6 Mikrocontroller-Beispiele • Zeitgeber und Ein-/Ausgabeeinheiten • 7 parallele Ein-/Ausgabeeinheiten, insgesamt 53 Bit • 2 synchrone serielle Ein-/Ausgabeeinheiten • 2 synchrone/asynchrone serielle Ein-/Ausgabeeinheiten • 2 8-Bit-Zähler/Zeitgeber mit Compare-Funktion und Pulsweitenmodulator • 2 16-Bit-Zähler/Zeitgeber mit Capture/Compare-Funktion und Pulsweitenmodulator • 1 Watchdog • 1 Analogvergleicher • 8 Digital/Analog-Wandlerkanäle, jeweils 10 Bit • 8-Bit-Erweiterungsbus im Daten-/Adressmultiplexing, 16 Bit Adressen • JTAG Test- und Debuginterface

2.6 Mikrocontroller-Beispiele 2.6.1.1 Prozessorkern Adress-, Daten- und Befehlsbusse des Prozessorkerns • Harvard Architektur • Direkte Verbindung zwischen ALU und Registersatz (RISC) • Befehlsadressraum 64kWorte = 128 kBytes • Taktfrequenz 8 MHz (ATmega128L) und 16 MHz (ATmega128)

2.6 Mikrocontroller-Beispiele Programmiermodell: • Load/Store-Architektur • RAMPZ (Bit0): Ansprechen der oberen oder unteren 64k Byte des Programmspeichers als Datum • RAMPX, RAMPY beim ATmega128 nicht vorhanden (Datenspeicher 64 kBytes)

2.6 Mikrocontroller-Beispiele Adressierungsarten: 2-Adress Format Rx = Rx + Ry (x, y {0 .. 31}) • Registerdirekt ADD R1,R0 R1 = R1 + R0 0C 10 • Unmittelbar SUBI R16,$10 R16 = R16 - 10h 51 00 • Adressdirekt LDS R1,($2000) R1 = (2000h) 50 10 20 00 • Registerindirekt LD R1,X R1 = (X) 90 1C • Registerindirekt LD R1,X+ R1 = (X), X++ 90 1D (Postinc, Predec)

2.6 Mikrocontroller-Beispiele • Registerindirekt LD R1,Y+5 R1 = (Y + 5) 80 15 (Displacement) • PC Relativ RJMP $10 PC = (PC + 10) C0 10 133 Befehle 8 und 16 Bit Ganzahl-Datentypen, Einzelbits Befehsbreite 16 Bit (Ausnahme adressdirekte Adressierung, dort 32 Bit)

2.6 Mikrocontroller-Beispiele SLEEP-Befehl für statisches Power-Management Betriebsarten: • Idle Mode: Prozessorkern abgeschaltet • ADC Noise Reduction Prozessorkern und Teil der Peripherie abgeschaltet • Power Save Mode Prozessorkern und alle Peripherie bis auf externe Unterbrechungen, Watchdog, eine serielle Schnittstelle und ein Zähler/Zeitgeber abgeschaltet • Power Down Mode wie Power Save, nur Zähler/Zeitgeber ebenfalls abgeschaltet • Standby Mode wie Power Down, aber Taktgenerator bleibt zum schnellen Wiederanfahren aktiv • Extended Standby Mode wie Power Save, aber Taktgenerator bleibt aktiv

2.6 Mikrocontroller-Beispiele 2.6.1.2. Unterbrechungsbehandlung • Einfacher Vektorinterrupt • Vektoren fest den Komponenten und 8 externen Interrupt- Eingängen zugeordnet • 35 Vektoren • 70 Byte Vektortabelle (16 Bit pro Eintrag = Adressbreite) • Vektortabelle am Anfang des Programmadressraums positioniert (0000h – 0044h), kann jedoch auch auf den Anfang des Boot-Bereiches verschoben werden • Feste Prioritäten, globales Maskenbit (I-Bit), jede Quelle kann jedoch durch Steuerregister auch individuell maskiert werden

2.6.1.3 Speicher und Adressraum Boot-Bereich: nur dort können Befehle zum Schreiben des FlashRAMs ausgeführt werden => generisches Ladeprogramm über serielle oder Debugschnittstelle dort ladbar

2.6 Mikrocontroller-Beispiele 2.6.1.4 EA-Einheiten, Zähler und Zeitgeber Digitale parallele EA

2.6 Mikrocontroller-Beispiele Digitale serielle EA Max. Baudrate USART: 250 kBaudSPI: 4 MBaudTwo Wire 400 kBaud max 128 Teilnehmer

2.6 Mikrocontroller-Beispiele Analog/Digital-Wandler • Wägeverfahren • 16 µsec Wandlungszeit • 10 Bit Auflösung • 8 Kanäle • Single oder Free Running Conversion Mode

2.6 Mikrocontroller-Beispiele Zählerund Zeitgeber Watchdog: 1 MHz Takt, 8 Stufen (214 – 221 = 14msec – 1,8sec) Modulator: Wahlweise Und bzw Oder Verknüpfungzweier Signale

2.6 Mikrocontroller-Beispiele Impulserzeuger: erzeugt zahlreiche Impulsformen bei Compare-Ereignis, z.B. Ausgang setzen, rücksetzen,wechseln,setzen bei Compare und rücksetzen bei max. Zählerstand, ...

2.6 Mikrocontroller-Beispiele 2.6.1.5 Erweiterungsbus • Kann über Steuerregister aktiviert und konfiguriert werden • Bei aktivem Erweiterungsbus sind die geteilten parallelen EA- Einheiten nicht verfügbar • Unterstützt variablen Adressraum • Die Adressbits A8 – A15 sind schrittweise zuschaltbar • Nicht benutzte Adressbits stehen den parallelen EA-Einheiten zur Verfügung • Wartezyklen (bis zu 3) beim Zugriff sind programmierbar

2.6 Mikrocontroller-Beispiele Aufbau des Erweiterungsbusses:

2.6 Mikrocontroller-Beispiele 2.6.2 PXA 255 – ein Hochleistungs-Mikrocontroller • 32 Bit Mikrocontroller • Weiterentwicklung der StrongARM Familie • ARM Version 5 RISC Prozessorkern • Vielfältige Peripherie • Wird z.B. gerne in Palmtops eingestetzt

2.6 Mikrocontroller-Beispiele • Prozessorkern • skalare RISC-Architektur ARM Version 5TE • Taktfrequenz bis 400 MHz • 32-Bit-Datenbus, 32-Bit-Adressbus • Virtuelle Speicherverwaltung für Daten und Befehle • 32 KBytes Befehls-Cache • 32 KBytes Daten-Cache • 2 KBytes Mini-Daten-Cache zur Aufnahme von Daten- strömen • Erweiterte Multiplikations-/Additionseinheit für Signalverar- beitung • komprimierbarer Befehlssatz • Ruhebetrieb

2.6 Mikrocontroller-Beispiele • Speicher • außer dem Cache kein weiterer integrierter Speicher • Schnittstelle für verschiedene Speichertypen (ROM, Flash-RAM, statisches RAM, dynamisches RAM, PC-Karten, ...) • Zeitgeber und Ein-/Ausgabeeinheiten • 85 Bit breite parallele Ein-/Ausgabe • 2 synchrone serielle Ein-/Ausgabeschnittstellen • 4 asynchrone serielle Ein-/Ausgabeschnittstelle, davon eine optimiert für den Bluetooth-Funkstandard • 1 serielle Infrarot-Schnittstelle • 1 USB-Schnittstelle

2.6 Mikrocontroller-Beispiele • Zeitgeber und Ein-/Ausgabeeinheiten (fortg.) • 1 serielle I2C-Schnittstelle • 1 serielle Audio-Schnittstelle (I2S) • 1 Audiocontroller • 1 LCD-Anzeigecontroller • 16 DMA-Kanäle • 1 Echtzeit-Zähler mit einer Compare-Einheit • 1 Zähler mit 4 Compare-Einheiten und Watchdog-Funktion • 2 Pulsweitenmodulatoren • vollständiger Erweiterungsbus mit 32 Bit Daten und 26 Bit Adressen

2.6 Mikrocontroller-Beispiele 2.6.2.1 Prozessorkern • Intel XScale Mikroarchitektur • 7-stufige skalare Pipeline • spekulative Befehlsausführung mit 2-Bit Sprungvorhersage • ARM Version 5 • Erweitert die im Vorgänger StrongARM verwendete ARM Version 4 um Codekompression und MAC-Einheit • Mehrere Registerbänke, die je nach Betriebsart gewechselt werden

2.6 Mikrocontroller-Beispiele Programmier-modell *: betriebsart- spezifisches Register

2.6 Mikrocontroller-Beispiele Besonderheiten des Befehlssatzes: • MAC-Einheit wie bei Signalprozessoren • 32-Bit Standard RISC Befehlssatz • 16-Bit komprimierter Thumb-Befehlssatz • Für RISC eher untypisch viele Adressierungsarten Vier Arbeitsmodi: • Turbo-Modus: hohe Taktfrequenz • Normaler Modus: niedere Taktfrequenz, Umschaltung zu hoher Taktfrequenz in Nanosekunden • Idle-Modus: Kern ist angehalten, Wecken durch Interrupt • Schlaf-Modus: Kern ist abgeschaltet, nur Peripherie wird noch mit Energie versorgt

2.6 Mikrocontroller-Beispiele 2.6.2.2. Unterbrechungsbehandlung • Einfaches Unterbrechungssystem mit festen Vektoren • 8 verschiedene Vektoren, davon 2 extern (IRQ, FIQ)

2.6 Mikrocontroller-Beispiele FIQ (Fast Interrupt) erlaubt eine etwas kürzere Reaktionszeit auf einen Interrupt als IRQ Grund: • Der Prozessorkern entnimmt der Vektortabelle nicht die Adresse der Behandlungsroutine • Vielmehr springt er auf die Tabellenadresse. Dort muss dann ein Sprungbefehl zur Behandlungsroutine stehen => eher Sprungtabelle als Vektortabelle • FIQ ist der letzte Eintrag der Tabelle. Daher muss hier kein Sprungbefehl stehen, die Behandlungsroutine kann sofort beginnen

2.6 Mikrocontroller-Beispiele Die Zuordnung der externen und internen Komponenten auf IRQ und FIQ erfolgt durch einen integrierten Interruptcontroller

2.6.2.3 Speicher und Adressraum außer Cache kein integrierter Speicher Externer Speicher ist in Bänken zu je 64 MBytes organisiert

2.6 Mikrocontroller-Beispiele 2.6.2.4 EA-Einheiten, Zähler und Zeitgeber Digitale parallele EA • 85 parallele E/A-Bits, Richtung einzelbitweise festlegbarJedes Bit kann als Interrupt-Eingang genutzt werden Digitale serielle EA • 4 asynchrone serielle Schnittstellen (Standard, Bluetooth, Modem, Hardware Handshake) • 2 synchrone serielle Schnittstellen • Spezielle serielle Schnittstellen (Fast Infrared, USB, I2C, I2S)

2.6 Mikrocontroller-Beispiele synchrone und spezielle serielle Schnittstellen

2.6 Mikrocontroller-Beispiele Stereo-Datenübertragung zwischen Audio-Bausteinen über die I2S Schnittstelle

2.6 Mikrocontroller-Beispiele • Audio-Controller (Abspielen und Aufnehmen von Audiosignalen im PCM-Format) • LCD Controller

2.6 Mikrocontroller-Beispiele Zähler und Zeitgeber (eher einfach, Controller mehr auf Kommunikations- denn Steuerungsaufgaben ausgelegt)

2.6 Mikrocontroller-Beispiele DMA-Controller 16 Kanäle, frei den internen und zwei externen Komponentenzuordenbar

2.6 Mikrocontroller-Beispiele Bedienung der DMA Gruppen im Round Robin Verfahren

2.6 Mikrocontroller-Beispiele 2.6.2.5 Erweiterungsbus • 26-Bit Adressbus • 32-Bit Datenbus • Steuerbus • zum Anschluss von 6 statischen Speicherbänken à 64 MBytes • zum Anschluss von 4 dynamischen Speicherbänken à 64 MBytes • zum Anschluss einer PC-Kartenschnittstelle (PCMCIA)

2.6 Mikrocontroller-Beispiele 2.6.3 MCore - optimiert für niedrigen Energieverbrauch • Architektur bzw. Mikroarchitektur eines Prozessorkerns • Primäres Ziel: niedriger Energieverbrauch • Wird in verschiedenen Mikrocontrollerns verwendet, z.B. MMC2001, MMC2003, MMC2107, MMC2114, ... Wir wollen uns hier auf die Energiespartechniken im Prozessorkern konzentrieren

2.6 Mikrocontroller-Beispiele Eigenschaften: • skalare RISC Architektur • Load/Store Konzept • 32 Bit Datenbus, Register und Ausführungseinheiten • 32 Bit Adressbus • Feste 16 Bit Befehlslänge • 4-stufige Pipeline • 2 Registersätze mit je 16 Registern zum schnellen Kontextwechsel • 8-, 16- und 32-Bit Datentypen • Statisches und dynamisches Power-Management • Statisches CMOS Design (bis 0 Hz Taktfrequenz) • 33 MHz maximale Taktfrequenz • 1,8 bis 3,6 Volt Versorgungsspannung

2.6 Mikrocontroller-Beispiele 2.6.3.1 Reduktion der Busaktivitäten und Erhöhung der Code-Dichte • Reduktion der ex-ternen Busaktivitätendurch reichhaltigenRegistersatz

2.6 Mikrocontroller-Beispiele • Hohe Code-Dichte durch 16-Bit Befehlssatz

2.6 Mikrocontroller-Beispiele 2.6.3.2 Statisches Power Management • Voll statisches Steuerwerk, bis zu 0 Hz Taktfrequenz • Niedere Versorgungsspannung von 1.8 Volt • Spezialbefehle und Ausgangssignale (LPMD = low power mode) um nicht benötigte Komponenten abzuschalten Modus (Befehl) LPMD1 LPMD0 Stop 0 0 Wait 0 1 Doze 1 0 Run 1 1

2.6 Mikrocontroller-Beispiele 2.6.3.3 Dynamisches Power Management • Power Aware Pipeline • Die Pipeline erkennt und deaktiviert gerade nicht benötigte Komponenten • Eine Addition aktiviert z.B. den Addierer, deaktiviert aber den Barrel-Shifter • Unterschiedliche Datengrößen werden unterstützt • Für 8 und 16 Bit Operationen werden unbenutzte Teile der internen 32 Bit Datenpfade und Verarbeitungseinheiten abgeschaltet

2.6 Mikrocontroller-Beispiele Gesamtverteilung des Energiebedarfs im Prozessorkern Taktleitungen: 36% des gesamten Energiebedarfs Datenpfade: 36% des gesamten Energiebedarfs Steuerlogik: 28% des gesamten Energiebedarfs => Optimierung der Taktleitungen und Sperrung von Teilen des Takt-Baumes (Clock Gating) kann viel Energie einsparen Die Pipeline sperrt z.B. den Takt für einige Komponenten während dem Auftreten von Pipeline-Hazards