Verilog

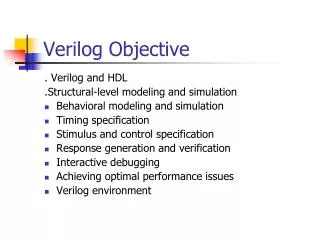

Verilog . ICT- SoC Lab. SOC Design Flow. Today (Language-based design ). In past (Schematic-based design). Source : Dynalith System. SOC Design Flow. Source : Dynalith System. HDL. Language-based design. Easy to design. Easy to simulate. Easy to reuse. Schematic-based design.

Verilog

E N D

Presentation Transcript

Verilog ICT-SoC Lab.

SOC Design Flow Today (Language-based design) In past (Schematic-based design) Source : Dynalith System

SOC Design Flow Source : Dynalith System

HDL Language-based design Easy to design Easy to simulate Easy to reuse Schematic-based design Source : University of Southampton

Verilog coding Coding using editor (Using notepad, any editor) Similar with C Easy to design, test System function Source : Dynalith System

Verilog Coding Needs for algorithm verification (hard to check in wave form) Checking fractional numbers in wave form ?

Simulation Before start coding a algorithm, make a simulator using high level language (C, C++, MATLAB) 1. Pre-design asystem hierarchy using Function level simulator 2. Accuracy and Performance of algorithms can be computed approximately 3. Can be a Comparison group of Verilog result (Ideal result)

Verilog Structure • Module name (Input, output list) • Port declaration; • Register declaration; Wire declaration; • Function • Assign • Function • Always • Module call • endmodule

Verilog Structure (i_a, i_b, c_in, o_sum, c_out) • Module name, in-out Input or output ? FA Blackbox

Verilog Structure i_a o_sum FA • Port declaration i_b c_out ? c_in

Verilog Structure (a_xor_b, a_and_b, ab_and_c) i_a o_sum FA i_b c_out ? • Wire declaration c_in

Verilog Structure a_xor_b i_a o_sum FA ab_and_c i_b c_out a_and_b c_in a_xor_b i_a o_sum i_b ab_and_c c_out a_and_b c_in • Design

Continuous assignment • Assign Statement • Continuous assignment • Assign a value to net • Structure • Assign Portorwire(Not register) = logical equation ; • Assign addr[15:0] = addr1_bits[15:0] ^ addr2_bits[15:0]; 16bit vector net16bit register • Bit operation • Use assign statement • ~ : not => assign Y = ~ A • &: and => assign Y = A & B • | : or => assign Y = A | B • ^ : xor => assign Y = A ^ B • ~^ : xnor => assign Y = A ~^ B

Vector < Code > i_A(3bit) i_B(3bit) o_and(3bit) and = i_D(2bit) o_or(2bit) i_C(4bit) or = i_E(2bit) o_xor(2bit) < Simulation > xor =

Bit extension < Code > i_A(2bit) i_B(2bit) o_C(4bit) < Simulation >

Number system <bit width>’<base><value> • Ex) • assign out_a = 8’d17 ; • out_a <= 16’h8B ;

2’s compliment • Signed-Magnitude System • Magnitude and Symbol ( ‘+’, ‘-’ ) • Applied to binary number by using ‘sign bit’ • Ex) Sign bit • Complement System • Negates a number by taking its complement • More difficult than changing the sign bit • Can be added or subtracted directly

2’s compliment • 510-310 = 210 • 510 = 001012 • -310 = 111012 • 001012 + 111012 000102 = 2 • 2’s Complementbit extension • If MSB is1, extend using 1, else 0 • Ex1) 111012=>111111012 • Ex2) 000112=>000000112 • A = 000102 • ~A = 111012 ~A+1 = 111012 • 000102 = 310 • 111012 = -310

Always & initial (Process) Module example(…); …… Initial … Initial begin … end always @(…) begin … end endmodule • Can operate Sequentiallyor concurrently • Eachalwaysand initial block operate concurrently • Within alwaysand initial block, statements are run sequentially • Initial statement (For initializing in simulation)

Blocking always @(posedgeclk) begin b=a; c=b; end Non-Blocking always @(posedgeclk) begin b<=a; c<=b; end • Blocking , Non-blocking Shifter

Blocking , Non-blocking < Code >

Module call F/A F/A F/A F/A i_a[0] i_b[0] i_a[1] i_b[1] i_a[2] i_b[2] i_a[3] i_b[3] c[0] c[1] c[2] c_out c_in Instance name Portmap o_sum[0] o_sum[1] o_sum[2] o_sum[3]

If, Case statement • Can only use in Always block Case statement If statement

16bit 2x1 MUX < Code > 16 i_A True (1) 2x1 MUX 0 1 16 o_C False (0) 16 i_B < Simulation > i_sel

2’s complement block module name : twos_com Input (8bit) : ref_data_8bit Output (16bit) : com_out • Convert input to 2’s complement value • and change the value to 16bit data Input ref_data_8bit 200 → -200 146 → -146 23 → -23 Output com_out

Absolute block module name : abs_mode Input (10bit) : abs_in Output (10bit) : abs_out • Take a absolute operation on INPUT data Input abs_in -118 → 118 -393 → 393 362 → 362 Output abs_out

Ripple carry adder • 4bit Ripple Carry Adder F/A F/A F/A F/A i_a[0] i_b[0] i_a[1] i_b[1] i_a[2] i_b[2] i_a[3] i_b[3] c[0] c[1] c[2] c_out c_in o_sum[0] o_sum[1] o_sum[2] o_sum[3]

Full adder a_xor_b ab_and_c a_and_b

F/A fa0 F/A fa1 F/A fa2 F/A fa3 i_a[0] i_b[0] i_a[1] i_b[1] i_a[2] i_b[2] i_a[3] i_b[3] c[0] c[1] c[2] c_out c_in o_sum[0] o_sum[1] o_sum[2] o_sum[3]