● CPLD 基础知识

● CPLD 基础知识. ● MAX+PLUSSII 简介. ● VHDL 语言. 兰州石化职业技术学院电子系. CPLD 技术应用. EDA 技术应用. 第 1 讲 前言及可编程逻辑器件. 使用对象: 专用集成电路 ASIC 的芯片设计研发人员 广大的电子线路设计人员 电子设计自动化 EDA ( Electronic Design Automation )技术是以大规模 可编程逻辑器件 为设计载体,通过 硬件描述语言 设计, EDA 软件 编译、仿真,最终 下载 到设计载体中,从而完成系统电路设计任务的新一代设计技术。. 一、前言.

● CPLD 基础知识

E N D

Presentation Transcript

● CPLD基础知识 ● MAX+PLUSSII简介 ● VHDL语言

兰州石化职业技术学院电子系 CPLD技术应用

EDA技术应用 第 1 讲 前言及可编程逻辑器件

使用对象: 专用集成电路ASIC的芯片设计研发人员 广大的电子线路设计人员 电子设计自动化EDA(Electronic Design Automation)技术是以大规模可编程逻辑器件为设计载体,通过硬件描述语言设计,EDA软件编译、仿真,最终下载到设计载体中,从而完成系统电路设计任务的新一代设计技术。 一、前言

EDA技术的发展及技术特色 EDA技术与计算机、集成电路、电子系统设计的发展密切相关,汇集了计算机科学领域的大多数最新研究成果,以高性能的计算机作为工作平台,开发出来的一整套电子设计系统软件。EDA技术经历了三个发展阶段。 • 20世纪70年代的计算机辅助设计(CAD)阶段。 • 20世纪80年代的计算机辅助工程设计(CAED)阶段。 • 20世纪90年代电子系统设计自动化(EDA)阶段。

20世纪70年代的计算机辅助设计(CAD)阶段 在这个阶段分别开发了一个个独立的软件工具,主要有电路原理图绘制、PCB(印刷电路板)图绘制、电路模拟、逻辑模拟等。 它们利用计算机的图形编辑、分析和计算等能力,协助工程师设计电子线路,使设计人员从大量繁琐、重复计算和绘图工作中解脱出来。 但总体来看自动化程度低,需要人工干预整个设计过程。美国Accel公司开发的Tango布线软件就是最具代表性的产品。

20世纪80年代的计算机辅助工程设计(CAED)阶段 这一阶段的EDA工具以逻辑模拟、定时分析、故障仿真、自动布局和布线为核心,重点解决电路设计完成之前的功能测试问题,代替了设计师的部分工作,利用这些工具,设计师能在产品制造之前预知产品的功能与性能。我们所熟悉的orCAD和Protel早期的版本是这一阶段中两种典型的设计工具。 但是大部分从原理图出发的EDA工具仍然不能适应复杂电子系统的设计要求,而具体化的元件图形制约着优化设计。

20世纪90年代电子系统设计自动化(EDA)阶段 20世纪90年代,设计师逐步从使用硬件转向设计硬件,从单个电子产品的开发转向系统级的电子产品开发SOC(System on a Chip,即片上系统集成)。 EDA工具是以系统级设计为核心,包括系统行为级描述与结构综合、系统仿真与测试验证、系统划分与指标分配、系统决策与文件生成等一整套的电子系统设计自动化工具。这时的EDA工具不仅具有电子系统设计的能力,而且还能提供独立于工艺和厂家的系统级设计,具有高级抽象的设计构思手段。 具备上述功能的EDA软件,可以使得电子工程师在不熟悉半导体工艺的情况下,完成电子系统的设计。

大规模可编程逻辑器件 三部分 硬件描述语言 EDA开发软件

二、可编程逻辑器件 ?PLD PLD能做什么呢?可以毫不夸张的讲,PLD能完成任何数字器件的功能,上至高性能CPU,下至简单的74电路,都可以用PLD来实现。PLD如同一张白纸或是一堆积木,工程师可以通过传统的原理图输入法,或是硬件描述语言自由的设计一个数字系统。通过软件仿真,我们可以事先验证设计的正确性。

2.1 可编程逻辑器件的分类 可编程逻辑器件按集成度分类

2.2 可编程逻辑器件的结构 与-或阵列结构(SPLD、CPLD) 查找表结构(FPGA)

2.3 基本PLD器件的原理结构图 与-或阵列结构

2.3 基本PLD器件的原理结构图 阵列线连接表示

2.3 基本PLD器件的原理结构图 1、输入缓冲器

2.3 基本PLD器件的原理结构图 2、可编程“与”阵列

2.3 基本PLD器件的原理结构图 3、可编程“或”阵列

2.3 基本PLD器件的原理结构图 可编程“与——或”阵列

2.3 基本PLD器件的原理结构图 6、输出电路 完成直接或寄存器输出及输出信号的反馈

2.3 基本PLD器件的原理结构图 一位加法器

2.4 简单可编程逻辑器件的特点 PROM(Programmable Read Only Memory)可编程只读存储器包括EPROM、EEROM。 PLA(Programmable Logic Array)可编程逻辑阵列 PAL(Programmable Array Logic)可编程阵列逻辑 GAL(Generic Array Logic)通用阵列逻辑

2.4 简单可编程逻辑器件的特点 4种SPLD器件的区别

2.4 简单可编程逻辑器件的特点 用PROM完成半加器逻辑阵列 1、PROM表达的PLD图阵列

2.4 简单可编程逻辑器件的特点 2、PLA逻辑阵列示意图

2.4 简单可编程逻辑器件的特点 PLA与 PROM的比较

2.4 简单可编程逻辑器件的特点 3、 PAL可编程阵列逻辑

2.4 简单可编程逻辑器件的特点 4、 GAL通用阵列逻辑 • General Array Logic Device • GAL的与阵列和PAL的类似 • 或阵列及输出寄存器则采用OLMC输出逻辑宏单元 • OLMC最多有8个或项,每个或项最多有32个与项 • 采用EEPROM技术,电擦除,可多次编程 • 可以取代中小规模数字集成电路和PAL器件

时钟信 号输入 输入口 GAL16V8 逻辑宏单元 输入/输出口 固定或阵列 可编程与阵列 三态控制

T 11 S 10 M 01 U Vcc 00 X G G AC 4 3 0 P ( n ) AC 0 1 T O I/O ( n ) G M 0 5 M 1 U ì G U G 1 X 1 2 í X 接或矩阵 D î XOR ( n ) 10 F 11 M 反馈 01 U 00 X 接零级输出 * AC ( m ) AC 1 OE 0 AC ( n ) CLOCK 1 GAL16V8的结构图 OLMC内部结构

2.4 LATTICE公司ispLSI 1032的结构和特点 • ispLSI 1032是ispLSI 1000系列中容量中等的器件,具备5V的在系统编程能力。 • 1. ispLSI 1032的主要特点: • 集成密度为6000等效门,192个寄存器; • 是电擦写CMOS(EEPROM)器件; • 有84个引脚,其中64个是I/O引脚,8个是专用输入引脚; • 最大工作频率 fmax = 125 MHz。

2.4 LATTICE公司ispLSI 1032的结构和特点 2. ispLSI 1032的结构框图——引脚图

2.4.1 LATTICE公司ispLSI 1032的结构和特点 3. ispLSI 1032的结构框图——功能框图

2.4 LATTICE公司ispLSI 1032的结构和特点 1) 集总布线区GRP(Global Routing Pool) 该区位于芯片的中央,其任务是将所有片内逻辑联系在一起

2.4 LATTICE公司ispLSI 1032的结构和特点 2) 万能逻辑块GLB(Generic Logic Block) GLB位于GRP的两边,每边8块,共32块

2.4 LATTICE公司ispLSI 1032的结构和特点 每个GLB由与阵列、乘积项共享阵列、四输出逻辑宏单元和控制逻辑组成。 GLB结构

2.4 LATTICE公司ispLSI 1032的结构和特点 GLB结构 • GLB的与阵列有18个输入端,其中16个来自集总布线区GRP,2个由I/O单元直通输入。 • 每个GLB有20个与门,形成20个乘积项,再通过4个或门输出。 • 4输出宏单元有4个触发器,可被组态为组合输出或寄存器输出(通过编程组态)。

2.4 LATTICE公司ispLSI 1032的结构和特点 3) 输入输出单元IOC(Input Output Cell) 输入输出单元IOC是功能框图最外层的小方块,共64个(IN0 ~ IN63)。该单元有输入、输出和双向I/O三类组态。可通过对控制输入输出三态缓冲器的使能端编程来选择

2.4 LATTICE公司ispLSI 1032的结构和特点 4) 输出布线区ORP(Output Routing Pool) • 输出布线区ORP是介于GLB和IOC之间的可编程互连阵列; • ORP的输入是8个GLB的32个输出端; • ORP的输出有16个,分别与该侧的16个IOC相连; • 通过对ORP编程,可以将任一个GLB输出灵活地送到16个I/O端的任何一个; • 在ORP的旁边还有16条通向GRP的总线,I/O单元可以使用,GLB的输出也可以通过ORP使用它,从而方便地实现了I/O端复用的功能和GLB之间的互连。

时钟分配网络CDN(Clock Distribution network) • CDN的输入信号由四个专用输入端Y0、Y1、Y2、Y4有提供; • CDN的输出有五个,其中CLK0、CLK1、CLK2提供给GLB,IOCLK0和IOCLK1提供给I/O单元; • 时钟专用GLB(B0)的四个输出送至CDN,以建立用户定义的内部时钟电路。

2.4 LATTICE公司ispLSI 1032的结构和特点 6) 大块结构(Megablock) • ispLSI 1032 采用了一种分块结构,每8个GLB连同对应的ORP、IOC等构成一个大块。 此外,每个大块中还包括2个专用输入端,仅供本大块内的GLB使用,靠软件自动分配。 • ispLSI 1032 共有4个大块。

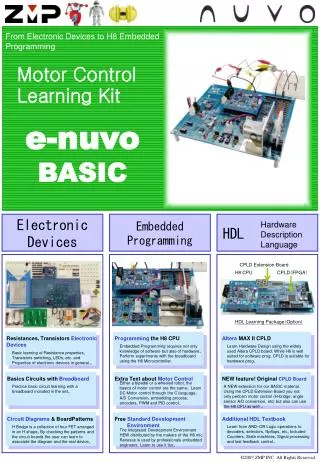

2.5 FPGA性能结构特点 2.5.1 FPGA-----现场可编程门阵列 (Field Programmable Gate Array) 1、可多次编程、改写、擦除 2、采用SRAM等编程技术 3、提供丰富的I/O端数和内部触发器,集成度远高于PAL和GAL 4、内部延时与器件结构和逻辑连接等有关,传输时延不可预测 5、由可编程逻辑模块阵列CLB、I/O模块和互连资源构成 6、查找表(Look-Up-Table)的原理与结构

2.5.1 FPGA性能结构特点 基于查找表的结构模块 查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。 目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有4位地址线的16x1的RAM。 当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能的结果,并把结果事先写入RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可

输入 A 输入 B 输入C 输入D 0 0 0 0 0 1 查找表 输出 16x1 RAM 1 0 0 0 0 0 0 0 1 1 2.5.1 FPGA性能结构特点 查找表原理 多路选择器

2.5.1 FPGA性能结构特点 例:F=abcd

2.6 CPLD性能特点 CPLD-----复杂可编程逻辑器件 (Complex Programmable Logic Device) 1、可多次编程、改写、擦除 2、采用CMOS EPROM、EEPROM、FLASH和SRAM等编程技术 3、I/O端数和内部触发器多达数百个,集成度远高于PAL和GAL 4、内部延时与器件结构和逻辑连接等无关,容易消除竞争和 冒 险 5、有多加密位,防止非法抄袭 6、采用分区阵列结构,每区相当于一PAL或GAL 7、基于乘积项(Product-Term)的PLD结构

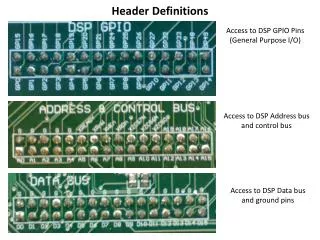

专用输入与全局信号 行连线带 行连线带 进位输入与级联输入 LAB局部连线 LAB控制信号 列到行连线带 列连线带 进位输出与级联输出 (1) 逻辑阵列LAB是由一系列的相邻LE构成的 列连线带

2.6.1 FLEX 10K系列FPGA结构图 (2) 逻辑单元LE 可编程寄存器 到快速互联通道 到LAB的局部互联

PLD/FPGA厂商概述 随着可编程逻辑器件应用的日益广泛,许多IC制造厂家涉足PLD/FPGA领域。目前世界上有十几家生产CPLD/FPGA的公司,最大的三家是: ALTERA,XILINX,Lattice,其中ALTERA和XILINX占有了60%以上的市场份额。