Multiplier

Multiplier. Lecture L7.3 Section 7.3. Multiplier. Binary Multiplication 4 x 4 Multiplier. Binary Multiplication. 9 C = 156. Binary Multiplication. 13 x 12 26 13 156. 1101 1100 0000 0000 1101 1101 10011100. Hex Multiplication. Hex Multiplication.

Multiplier

E N D

Presentation Transcript

Multiplier Lecture L7.3 Section 7.3

Multiplier • Binary Multiplication • 4 x 4 Multiplier

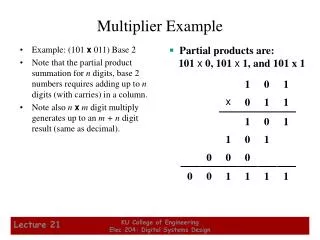

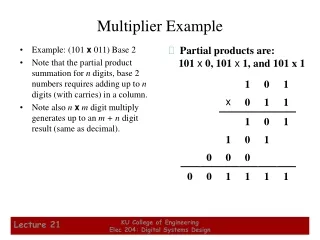

9 C = 156 Binary Multiplication 13 x 12 26 13 156 1101 1100 0000 0000 1101 1101 10011100

Hex Multiplication Dec Hex 3D x 5A 262 A x D = 82, A x 3 = 1E + 8 = 26 131 5 x D = 41, 5 x 3 = F + 4 = 13 157216 = 549010 61 x 90 5490

A 4x4 Array Multiplier 1101 1100 0000 0000 1101 1101 10011100 B3 B2 B1 B0 A3 A2 A1 A0 p3 p2 p1 p0 p3 p2 p1 p0 p3 p2 p1 p0 p3 p2 p1 p0 P7 P6 P5 P4 P3 P2 P1 P0

MODULE pprod interface(Ai,[B3..B0] -> [p3..p0]); TITLE '4-bit partial product' DECLARATIONS " INPUT PINS " Ai PIN; " 1-bit multiplier B3..B0 PIN; B = [B3..B0]; " 4-bit multiplicand " OUTPUT PINS " p3..p0 PIN ISTYPE 'com'; p = [p3..p0]; " 4-bit partial product EQUATIONS p = Ai & B; END pprod

MODULE mult4 TITLE '4-bit multiplier' DECLARATIONS hex7seg interface([D3..D0] -> [a,b,c,d,e,f,g]); d7L FUNCTIONAL_BLOCK hex7seg; d7R FUNCTIONAL_BLOCK hex7seg; pprod interface(Ai,[B3..B0] -> [p3..p0]); pp0 FUNCTIONAL_BLOCK pprod; pp1 FUNCTIONAL_BLOCK pprod; pp2 FUNCTIONAL_BLOCK pprod; pp3 FUNCTIONAL_BLOCK pprod; adder interface([A3..A0],[B3..B0] -> [S3..S0],CF); ad1 FUNCTIONAL_BLOCK adder; ad2 FUNCTIONAL_BLOCK adder; ad3 FUNCTIONAL_BLOCK adder;

" INPUT PINS " A3..A0 PIN 11,7,6,5; " Left Switches S6 - 1..4 A = [A3..A0]; " 4-bit multiplicand B3..B0 PIN 4,3,2,1; " Right Switches S7 - 1..4 B = [B3..B0]; " 4-bit multiplier " INTERMEDIATE NODES P7..P0 NODE ISTYPE 'com'; P = [P7..P0]; " 8-bit product " OUTPUT PINS " [a,b,c,d,e,f,g] PIN 57,58,61,62,63,65,66,67 ISTYPE 'com'; "Leftmost (tens) 7-segment LED display [aa,bb,cc,dd,ee,ff,gg] PIN 15,18,23,21,19,14,17,24 ISTYPE 'com'; " Rightmost (units) 7-segment LED display

EQUATIONS pp0.[B3..B0] = [B3..B0]; pp0.Ai = A0; pp1.[B3..B0] = [B3..B0]; pp1.Ai = A1; pp2.[B3..B0] = [B3..B0]; pp2.Ai = A2; pp3.[B3..B0] = [B3..B0]; pp3.Ai = A3;

ad1.[A3..A0] = pp1.[p3..p0]; ad1.[B2..B0] = pp0.[p3..p1]; ad1.B3 = 0; ad2.[A3..A0] = pp2.[p3..p0]; ad2.[B2..B0] = ad1.[S3..S1]; ad2.B3 = ad1.CF; ad3.[A3..A0] = pp3.[p3..p0]; ad3.[B2..B0] = ad2.[S3..S1]; ad3.B3 = ad2.CF;

P0 = pp0.p0; P1 = ad1.S0; P2 = ad2.S0; [P6..P3] = ad3.[S3..S0]; P7 = ad3.CF;

[a,b,c,d,e,f,g,dp] = d7L.[a,b,c,d,e,f,g,dp]; d7L.[D3..D0] = [P7..P4]; [aa,bb,cc,dd,ee,ff,gg,dpp] = d7R.[a,b,c,d,e,f,g,dp]; d7R.[D3..D0] = [P3..P0]; @radix 16; test_vectors ([A,B] -> P) [6,6] -> 24; [0A,0B] -> 6E; [5,9] -> 2D; [0C,0F] -> 0B4; [0F,0F] -> 0E1; END mult4