I RS

I RS. INTEGRISANI RAČUNARSKI SISTEMI 1. deo 2014. Autor : Nenad Jovičić. Sadržaj vežbi. Računske vežbe: kroz nekoliko konkretnih projektnih zadataka biće: opisane najčešće korišćene periferije objašnjeno podešavanja tih periferija napisani programi koji obavljaju tražene funkcije

I RS

E N D

Presentation Transcript

IRS INTEGRISANI RAČUNARSKI SISTEMI 1. deo 2014 Autor: NenadJovičić

Sadržaj vežbi • Računske vežbe: • kroz nekoliko konkretnih projektnih zadataka biće: • opisane najčešće korišćene periferije • objašnjeno podešavanja tih periferija • napisani programi koji obavljaju tražene funkcije • prikazane osnovne tehnike rada sa razvojnim okruženjem. • Laboratorijske vežbe: • 3 laboratorijske vežbe, svaka sa trajanjem do 4 sata, • Izvode se u laboratoriji 18 na realnom hardveru, povezanom sa PC-jem i razvojnim okruženjem preko FET debugger-a. • Informacije u vezivežbi: tnt.etf.rs/~oe4irs

Razvojno okruženje za pisanje softvera Za potrebe razvoja softvera koristi se razvojno okruženje IAR Embedded Workbench. Kickstart verzija koja podržava pisanje svih aplikacija koje će biti razvijane u okviru kursa se može download-ovati sa sajta www.iar.com. U okviru paketa integrisani su editor, asembler, C kompajler, softverski simulator, kao i podvarijanta simulatora koja zajedno sa FET debugger-om čini emulator.

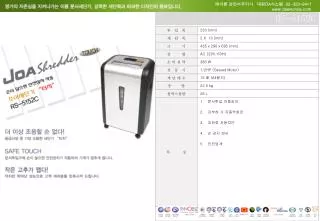

Razvojnisistem RS_MSP430F449 • Sistemimapunomogućnosti i puno komponenti. Detaljna šema je dostupna na: http://tnt.etf.rs/~oe4irs/RS_MSP430_sch.pdf

MSP430Fxxx Familija MSP430 se deli na nekoliko podfamilija: MSP430x4x, MSP430x3x... Mi radimo sa mikrokontrolerom MSP430F449, koji spada u podfamiliju MSP430x4x. MSP430F449 ima “samo” 60k Flash memorije i 2k RAM memorije…ali to nije tako malo s obzirom na namenu… Dokumentacija o podfamiliji MSP430x4xx se nalazi na adresi: http://tnt.etf.rs/~oe4irs/slau056e-msp430F4xx.pdf Dokumentacija o konkretnom mikrokontroleru MSP430F449 se nalazi na adresi: http://tnt.etf.rs/~oe4irs/msp430F449.pdf

Projektni zadatak 1 Napisatiasemblerskiprojekatza razvojni sistem RS-MSP430F449 kojinakomandupritiskatastera BCD sadržajregistra R12 ispisuje na jedan sedmosegmentni displej. Istovremeno, dok je taster pritisnut jedna LE dioda treba da svetli i obrnuto. Projekat treba da se sastoji iz jednog fajla asm.s43 u kome se nalazi glavni program koji testira pritisak tastera i fajla function.s43 u kome se nalazi funkcija za ispis sadržaja registra na displej WriteLed

Opis hardvera Razvojni sistem RS-MSP430 poseduje više funkcionalnih celina od kojih su one interesantne za ovaj projekat prikazane na slici

Organizacija softvera • Pisanje dobrog softvera podrazumeva njegovu podelu na logičke celine, zgodne za samostalnu implementaciju. • Ovaj projektni zadatak se može podeliti na nekoliko programskih celina: • Inicijalizacija resursa mikrokontrolera • Deo glavnog programa koji vrši očitavanje tastera • Funkcija koja vrši uključivanje diode • Funkcija koja vrši ispis sadržaja registra R12 na sedmosegmentni displej

Kreiranje projekta S obzirom da je tražena asemblerska implementacija u dijalogu kreiranja projekta se izabira čist asemblerski projekat

Osnovni fajl Predefinisani Template za asemblerski projekat je prikazan na slici

Hardverske specifičnosti Msp430.h je opšti “include” fajl za celu MSP430

Hardverske specifičnosti Unutar fajla Msp430.h se vrši dalja redirekcija na posebno izabran mikrokontroler

Include fajl Korišćenje pojmova definisanih u “include” fajlu olakšava kodiranje ali i kasniji prelaz sa jednog na drugi mikrokontroler

Program – niz asemblerskih instrukcija • U ovom projektu biće korišćene instrukcije za: • pristup portovima, • ispitivanje uslova, • instrukcije uslovnih skokova • i instrukcije za poziv i povratak iz potprograma.

Glavni program S obzirom na tražene zahteve po pitanju funkcionalnosti, dijagram toka programa bi trebalo da izgleda ovako

Glavni program – detekcija pritiska tastera • Algoritam detekcije pritiska tastera se zasniva na detekciji opadajuće ivice na ulaznom pin-u • Glavni program mikrokontrolera treba ciklično (periodično) da očitava stanje ulaznog pin-a,poredi ga sa vrednošću iz prethodnog očitavanja i u slučaju detekcije prelaska sa 1 na 0 izvršava zahtevanu radnju. U ovom projektu zahteva se ispis sadržaja registra R10 da sedmosegmentni displej.

Digitalni portovi • Svaki port se kontrolišesačetiriregistra • PxIN – ulazniregistar (x=1-6) • Očitani bit =0 – naulazu je nizaklogičkinivo • Očitani bit =1 – naulazu je visoklogičkinivo • PxOUT – izlazniregistar (x=1-6) • upisani bit =0 – naizlazu je nizaklogičkinivo • upisani bit =1 – naizlazu je visoklogičkinivo • PxDIR – registarselekcijeulazailiizlaza (x=1-6) • upisani bit =0 – pin je ulazni • upisani bit =1 – pin je izlazni • PxSEL – registarselekcijealternativnihfunkcija (x=1-6) • upisani bit =0 – ulazno/izlaznafunkcijapina • upisani bit =1 – alternativnafunkcijadodeljenanekojperiferiji

Glavni program - kod Glavni program

BIT instrukcija BIT instrukcija se koristi za testiranje stanja bita u registru.

BIS i BIC instrukcije Koriste se za Set-ovanje/Clear-ovanje pojedinačnog bita u registru.

XOR instrukcija Logička instrukcija koja xor-uje podatak sa konstantom.

AND instrukcija Instrukcija koja vrši logičko I dva podatka.

Instrukcije uslovnih skokova JZ i JNZ Ove instrukcije izvršavaju ili ne skok u zavisnosti od stanja flag-a u SR.

Bezuslovni skok JMP Bezuslovni skok na adresu.

Direktive asemblera Program predstavlja niz asemblerskih instrukcija i podataka smeštenih negde u memoriji. Da bi se asembleru reklo gde se i na koji način smeštaju ti blokovi instrukcija ili podataka koriste se direktive asemblera Direktive asemblera su instrukcije kojima programer vodi asembler u cilju prevođenja asemblerskog koda na odgovarajući željeni način

Asembliranje Asembliranje je proces prevodjenja asemblerskog (simboličkog) u mašinski kod. Alatka koja to radi se zove asembler. Da bi proces bio izveden na odgovarajući način potrebno je podesiti odgovarajuće opcije.

Proces asembliranja Izveštaj o procesu asembliranja nalazi se u tzv. list fajlu.

Linkovanje Linkovanje je proces u kome se mašinski kod iz različitih asemblerskih fajlova prevodi u jedan jedinstvenfajl koji se može spustiti u memoriju mikrokontrolera. Sama reč “link” ukazuje da se radi o povezivanju odvojenih delova, u našem slučaju glavnog programa i potrporgrama u jedinstvenu celinu.

Linkovanje Najvažnija uputstva za linker se nalaze u “linker command file”-u

Linkovanje Izveštaj o radu linkera se nalazi u tzv. map fajlu. U njemu je mapiran položaj blokova podataka ili koda u memoriji.

Linkovanje U linker fajlu se daje i pregled zauzetosti memorije.

Kompajliranje Komanda MAKE vrši kompajliranje i linkovanje projekta.

Debagovanje Debagovanje je proces u kome se uz pomoć softverskog simulatora, ili harverskog debagera vrši testiranje aplikacije.

Debug-ovanje Debagovanje u simulatoru podrazumeva simulaciju spoljašnjih događaja relevenatnih za projekat. Dobra simulacija je ona koja najvernije simulira spoljašnje događaje. U našem slučaju radi se o simulaciji pritiska na taster S4, koji se očitava preko bita 2 porta P1. Najjednostavniji i najpregledniji vid simulacije je single steping. Problem je što to može dugo da potraje i zamorno je. Mnogo efikasniji vid debagovanja je postavljanjem Brekapoint-a na “dobra” mesta. Generalno Breakpoint se postavlja tamo gde treba simulirati spoljnji događaj preko registra (u našen slučaju pritisak tastera), i tamo gde se očekuje reakcija na taj događaj.

Drugačiji pristup - prekidi • Prekidi koji se generišu promenom stanja ulaznih pinova portova P1 i P2 se kontrolišu preko tri registra • PxIFG – registar flegova (x=1,2) • Očitani bit =0 – na tom pinu se nije dogodila promena koji izaziva prekid • Očitani bit =1 – na tom pinu se dogodila promena koji izaziva prekid • PxES – registar selekcije ivice (x=1,2) • upisani bit =0 – prekid se događa na rastuću ivicu signala na tom pinu • upisani bit =1 – prekid se događa na opadajuću ivicu signala na tom pinu • PxIE – registar dozvole prekida (x=1,2) • upisani bit =0 – prekid nije dozvoljen za promenu stanja na tom pinu • upisani bit =1 – prekid je dozvoljen za promenu stanja na tom pinu

Tabela vektora prekida – MSP430F449 http://tnt.etf.rs/~oe4irs/msp430F449.pdf