Understanding Flip-Flops and Latches: Timing Constraints and Edge Sensitivity

Learn about combinational logic circuits: RS latches, D latches, JK latches, master-slave flip-flops, and D flip-flops. Understand timing constraints, setups, holds, and edge sensitivity in digital electronics.

Understanding Flip-Flops and Latches: Timing Constraints and Edge Sensitivity

E N D

Presentation Transcript

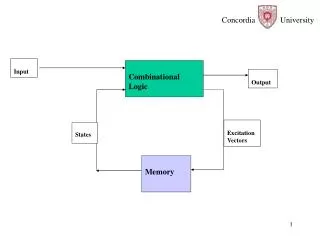

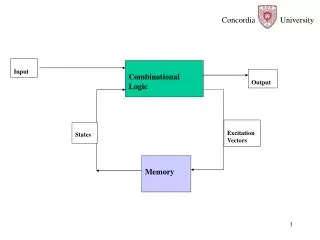

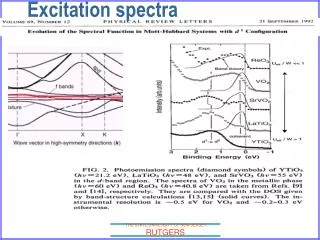

Input Combinational Logic Output Excitation Vectors States Memory

RS Latch Q+ = S + R’ Q Two Problems: R=S= 1 Not allowed, Data is transparent

The D Latch Problem: Level sensitive

JK Latch : Universal, Level sensitive, Timing Constraints due to feed back.

Master Slave Flip Flop Edge sensitive,Set up and Hold time

Master Slave Flip Flop Edge sensitive,-Falling Edge Set Up and Hold Time constraints Path to setup data Master Slave Q Q Q D D D D D Latch Latch Q C C C Path to hold data D C Q

Edge triggered Flip Flop: Set up and Hold time Constraints

Edge Triggered, D Flip Flop NAND1 S Q NAND2 NAND5 clk R NAND3 NAND6 D NAND4 reset

NAND1 S Q NAND2 NAND5 clk R NAND3 NAND6 D NAND4 reset When CLK changes from 0 to 1 Case1, D=0: tsetup= t4, thold=t3 Case2, D=1 tsetup=t4 + t1 thold= t2

NAND1 S Q NAND2 NAND5 clk R NAND3 NAND6 D NAND4 reset When CLK changes from 0 to 1 Case1, D=0: tsetup= t4, thold=t3 Path for hold Path for set up

NAND1 S Q NAND2 NAND5 clk R NAND3 NAND6 D NAND4 reset When CLK changes from 0 to 1 Case2, D=1 tsetup=t4 + t1 thold= t2 Path to set up Path to hold