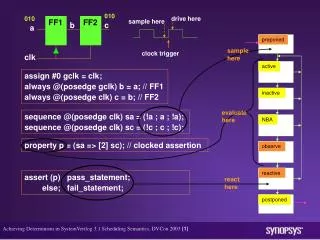

Reactive Clocked Assertion Example in SystemVerilog

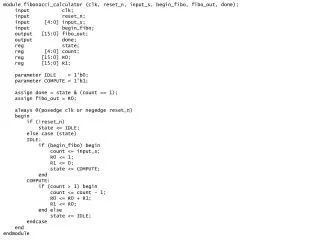

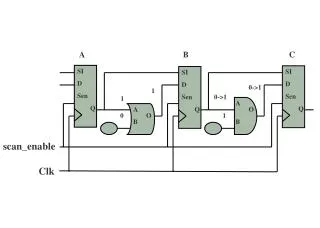

This example showcases a reactive clocked assertion in SystemVerilog with two flip-flops, FF1 and FF2. The design utilizes a clock trigger to evaluate properties based on the states of two signals, 'sa' and 'sc'. When 'a' is asserted or deasserted, it affects the state of 'b', which in turn influences 'c'. A property 'p' is defined that specifies the relationship between 'sa' and 'sc', with the assertion reacting to changes on the positive edge of the clock. The example includes pass and fail statements for successful or unsuccessful assertion evaluations.

Reactive Clocked Assertion Example in SystemVerilog

E N D

Presentation Transcript

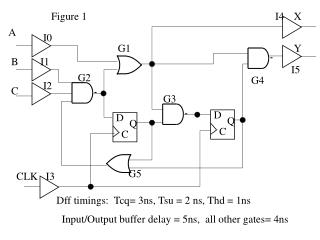

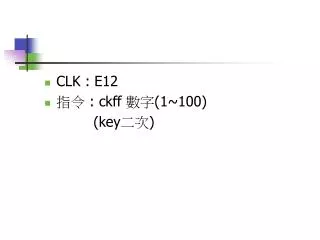

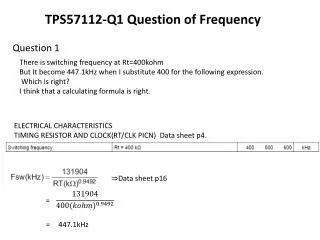

010 010 drive here sample here sample here clock trigger evaluate here sequence @(posedge clk) sa = (!a ; a ; !a); sequence @(posedge clk) sc = (!c ; c ; !c); property p = (sa => [2] sc); // clocked assertion reactive react here FF1 FF2 b c a preponed clk active assign #0 gclk = clk; always @(posedge gclk) b = a; // FF1 always @(posedge clk) c = b; // FF2 inactive NBA observe assert (p) pass_statement; else; fail_statement; postponed