Computer System Organization

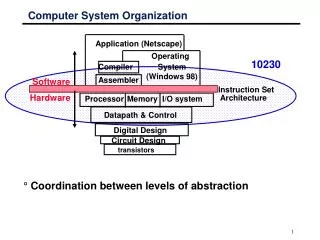

Computer System Organization. Application (Netscape). Coordination between levels of abstraction. Operating. 10230. Compiler. System (Windows 98). Software. Assembler. Instruction Set Architecture. Hardware. Processor. Memory. I/O system. Datapath & Control. Digital Design.

Computer System Organization

E N D

Presentation Transcript

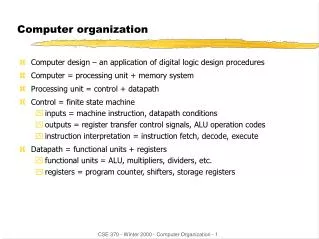

Computer System Organization Application (Netscape) • Coordination between levels of abstraction Operating 10230 Compiler System (Windows 98) Software Assembler Instruction Set Architecture Hardware Processor Memory I/O system Datapath & Control Digital Design Circuit Design transistors

Abstraction Levels of a Computer System • Application S/W • MS Word computer as electronic type-writer • MS Excel computer as electronic calculator • System S/W • Compilers computer as translator (source to executable program) • Operating Systems computer as machine that executes programs, stores files, prints content of files to printers, communicate with other computers • Instruction Set • What basic operations can be carried out • What, where, and how data can be stored & retrieved in/from memory • How can data be exchanged to the outside “world” • Computer H/W • The 5 components: Datapath, Control, Memory, Input, Output

Levels of Programming Languages A = 25; B = 8; C = A * B; A dw 25 B dw 8 C resw 1 mov eax, [A] mov ebx, [B] add eax, ebx mov [C], eax High Level Language Program (e.g., C) 10230 Compiler Assembly Language Program Assembler Machine Language Program (80x86) 0000 1001 1100 0110 1010 1111 0101 1000 1010 1111 0101 1000 0000 1001 1100 0110 1100 0110 1010 1111 0101 1000 0000 1001 0101 1000 0000 1001 1100 0110 1010 1111 Machine Interpretation Control Signal Specification ° °

Java: Interpreted Programming Language Java Language Program Java Compiler Byte Code Interpreter (Java Virtual Machine) + Just In Time (JIT) Compiler Machine Language Program (80x86) Machine Interpretation Control Signal Specification ° °

Components of a Computer MONITOR: to output data “CPU”: to process command & data SPEAKER: to output data DISK: to input/output data KEYBOARD: to input command/data MOUSE: to input command/data

Keyboard, Mouse Computer Processor (active) Memory (passive) (where programs, data live when running) Devices Disk(where programs, data live when not running) Input Control (“brain”) Datapath (“brawn”) Output Display, Printer Five main components of a computer “CPU”

Processor • Responsible of executing program stored in memory • read instructions & input data • execute • store results (output data) • Datapath (“muscle”): • ALU: Aritmetic & Logical Unit • Exposed register • Size of register determines processor smallest data unit (i.e., 8-bit, 16-bit, 32-bit, 64-bit computers) • Hidden register • Control Unit (“brain”): • interprete instruction • control data transfer between registers • define processsor’s ‘language’ complexity (e.g., RISC vs. CISC)

Memory • Responsible of storing instructions/data • Each unit of instruction/data is stored in a memory cell, whose address is known to the processor • Any memory cell can be accessed by a processor randomly (RAM: random access memory) • The amount of instruction/data accessed by a processor may vary (1, 2, ..., n memory cells at a time) • To achieve trade-off between speed and cost, memory is structured hierarchically memory hierarchy

Input/Output (Device) • Responsible of communicating with the outside (of computer) world • A device may serve as Input-only, Output-only, or both (Input-Output) device • Input-only: keyboard • Output-only: monitor display • Input-Output: floppy disk, hard disk • Data translation may be needed when processor exchanges data with an I/O device so humans can understand them

Interconnection between components Gbr. 5. (a) back view (b) side view *Taken from http://www.ui.ac.id/pdpt/ppkk/PengenalanKomputer.html

Interconnections between components Proc Caches Processor-Memory Bus adapters I/O Bus Memory Controllers Disks Displays Keyboards I/O Devices: Networks Interconnected by a BUS

Technology Trend: Microprocessor Capacity Pentium 4: 42 million Pentium III: 9.5 million Alpha 21264: 15 million Pentium Pro: 5.5 million PowerPC 620: 6.9 million Alpha 21164: 9.3 million Sparc Ultra: 5.2 million Moore’s Law 2X transistors/Chip Every 1.5 years Called “Moore’s Law”

Technology Trend: Memory Capacity (1 Chip DRAM) year size(MB) 1980 0.0625 1983 0.25 1986 1 1989 4 1992 16 1996 64 2000 256 Now 1.4X/yr, or doubling every 2 years 4000X since 1980

Technology Trend: Disk Capacity • Areal Density =BPI x TPI • BPI: Bit Per Inch • TPI: Tracks Per Inch • Change slope 30%/yr to 60%/yr about 1991

Intel Pentium Pro Quad • All coherence and multiprocessing glue in processor module • Highly integrated, targeted at high volume • Low latency and bandwidth

SUN Enterprise • Proc + mem card - I/O card • 16 cards of either type • All memory accessed over bus, so symmetric • Higher bandwidth, higher latency bus

Cray T3E • Scale up to 1024 processors, 480MB/s links • Memory controller generates request message for non-local references • No hardware mechanism for coherence • SGI Origin etc. provide this

IBM SP-2 • Made out of essentially complete RS6000 workstations • Network interface integrated in I/O bus (bw limited by I/O bus)

Berkeley NOW • 100 Sun Ultra2 workstations • Inteligent network interface • proc + mem • Myrinet Network • 160 MB/s per link • 300 ns per hop

Intel History: ISA evolved since 1978 • 8086: 16-bit, all internal registers 16 bits wide; no general purpose registers; ‘78 • 8087: + 60 Fl. Pt. instructions, (Prof. Kahan) adds 80-bit-wide stack, but no registers; ‘80 • 80286: adds elaborate protection model; ‘82 • 80386: 32-bit; converts 8 16-bit registers into 8 32-bit general purpose registers; new addressing modes; adds paging; ‘85 • 80486, Pentium, Pentium II: + 4 instructions • MMX: + 57 instructions for multimedia; ‘97 • Pentium III: +70 instructions for multimedia; ‘99 • Pentium 4: +144 instructions for multimedia; '00

Architecture of Intel P6 (Pentium Pro) Control Unit Data Path

Example: Pentium-based Computer Processor Processor/Memory Bus Memory PCI Bus I/O I/O Busses