ECE 371 – Unit 18

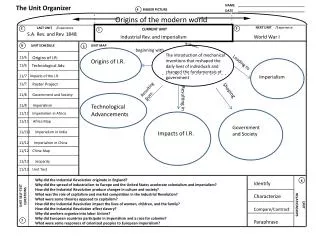

ECE 371 – Unit 18. Pulse Width Modulation. Pulse Width Modulation (Uses Port P pins). PWM Overview. Td. T. T = Period Duty Cycle = (Td/T)*100% T is usually a constant, Information is carried in Pulse Width Td. 4 Ways to Generate the Clock Input for the PWM System. Clock A Clock SA

ECE 371 – Unit 18

E N D

Presentation Transcript

ECE 371 – Unit 18 Pulse Width Modulation

PWM Overview Td T T = Period Duty Cycle = (Td/T)*100% T is usually a constant, Information is carried in Pulse Width Td

4 Ways to Generate the Clock Input for the PWM System Clock A Clock SA Clock SB Clock B Prescaler A Scale A Register Bus Clock Prescaler B Scale B Register

• Channels 0, 1, 4, and 5 Get Clock A or Clock SA • Channels 2, 3, 7, and 8 Get Clock B or Clock SB

Clock A and B Prescale Select Pre-scale Option for Clock B Select Pre-scale Option for Clock A

Clock A and B Prescaler Select Bus Clock = 2,000,000 Hertz

Clock SB Generation Clock SB = Clock B/(2*PWMSCLB) PWMSCLB=0 is considered 256

Clock Selection Clock B or SB -> Channels 2, 3, 6, 7 Clock A or SA -> Channels 0, 1, 4, 5

Three 8-Bit Registers for Each PWM Channel • PWMCNTx: Counter • PWMPERx: Period select • PWMDTYx: “Duty” time (Time from beginning of cycle and the first polarity switch)

Duty Registers Double Buffered

Three Control Bits for Each PWM Channel • PWMEx: Enable • PPOLx: Polarity (starting value in each PWM cycle) • CAEx: Center Alignment Enable

PPOLx – Pulse Width Channel x Polarity 1 = PWM Channel x output is high at the beginning of the period, then goes low when the duty count is reached. 0 = PWM Channel x output is low at the beginning of the period, then goes high when the duty count is reached

Center Alignment Selection CAEx – Center Aligned Output Mode on Channel x 1 = Channel x operates in Center Aligned Output Mode 0 = Channel x operates in Left Aligned Output Mode

#define PWME _P( 0xA0) #define PWMPOL _P(0xA1) #define PWMCLK _P(0xA2) #define PWMPRCLK _P(0xA3) #define PWMCAE _P(0xA4) #define PWMCTL _P(0xA5) #define PWMSCLA _P(0xA8) #define PWMSCLB _P(0xA9) #define PWMCNT0 _P(0xAC) #define PWMCNT1 _P(0xAD) #define PWMCNT2 _P(0xAE) #define PWMCNT3 _P(0xAF) #define PWMCNT4 _P(0xB0) #define PWMCNT5 _P(0xB1) #define PWMCNT6 _P(0xB2) #define PWMCNT7 _P(0xB3)

#define PWMPER0 _P(0xB4) #define PWMPER1 _P(0xB5) #define PWMPER2 _P(0xB6) #define PWMPER3 _P(0xB7) #define PWMPER4 _P(0xB8) #define PWMPER5 _P(0xB9) #define PWMPER6 _P(0xBA) #define PWMPER7 _P(0xBB) #define PWMDTY1 _P(0xBC) #define PWMDTY2 _P(0xBD) #define PWMDTY3 _P(0xBE) #define PWMDTY4 _P(0xBF) #define PWMDTY5 _P(0xC0) #define PWMDTY6 _P(0xC1) #define PWMDTY7 _P(0xC2)

Example – PWM0 • Port P is PWM Modulation Pins • Port P Pin 0 = PWM0 Pin – Set for Output • DDRP = DDRP |0x01;

Example – PWM0 • Typical choice of PWM Period: 250 (max is 255--want large value to get good time resolution in selection of duty cycle) • Bus clock = 2 MHZ • Assume Desired Frequency of PWM = 10 Hz • Design task: Select Pre-scaler Value ( 1, 2, 4, 8, 16, 32, 64, or 128) and Scale Value (1 ≤ SV ≤ 256)

Example (cont. 1) • PWM freq = 2 x 106 2 (SV) (PV) Period = 10 • Let Period = 250 and try PV = 1, and solve for SV: 105 250 SV = = 400 However, largest possible value of SV is 256. Therefore, we can choose PV = 2 and SV = 200.

Example (cont. 1.5) More general approach: • PWM freq = 2 x 106 2 (SV) (PV) Period • Let Period = 250 (and PWM Freq = 1-) and solve for the Product of (SV)(PV): 105 250 (SV)(PV) = = 400 Possible Values of SV: 1, 2, 3, , , , 256 Possible Values of PV: 1, 2, 4, 8, 16, 32, 64, 128 Several solutions, e.g., (PV = 2, SV = 200), (PV = 4, SV = 100), (PV = 8, SV = 50),

Example (cont. 3.1) • Select Prescale Value of 2 for Clock A • PWMPRCLK = (PWMPRCLK&0xF8)|0x01; PWMPRCLK PCKA2 PCKA1 PCKA0 PCKB2 PCKB1 PCKB0 0 0 1 SELECT DIVISION BY 2

Example (cont. 3.15) • Select “Scale A” Value of 200 • PWMSCLA = 200;

Example (cont. 3.2) • Select SA Clock for Channel 0 (since using both scalers) • PWMCLK = PWMCLK | 0x01; PWMCLK PCLK6 PCLK7 PCLK5 PCLK4 PCLK3 PCLK2 PCLK1 PCLK0

Example (cont. 3.3) • Select Left Alignment • PWMCAE = PWMCAE & 0XFE; PWMCAE CAES7 CAES6 CAES5 CAES4 CAES3 CAES2 CAES1 CAES0 1: Center Aligned 0: Left Aligned

Example (cont. 4) • Select Polarity (choose initially High) • PWMPOL = (PWMPOL&0xFE)|0x01; • Select Duty Cycle to be 50% • PWDTY0 = 125; • Enable PWM0 • PWME = PWME | 0x01;

Waveform PM0 .05 Sec .1 Sec.