Architecture

This document presents innovative designs and prototypes for low-power wireless sensor networks developed at UC Berkeley and Intel Research. It details the evolution of various mote prototypes, such as the MICA and weC Mote, focusing on their architectures, low-power listening strategies, time synchronization techniques, and localization methods. Highlighting the necessity of distributed time synchronization and error noise mitigation, it emphasizes cross-layer optimizations to enhance communication efficiency. The end goal is to build compact, cost-effective mote solutions that cater to diverse applications while maintaining performance.

Architecture

E N D

Presentation Transcript

Architecture David Culler University of California, Berkeley Intel Research Berkeley http://webs.cs.berkeley.edu

Design Lineage • COTS dust prototypes (Kris Pister et al.) • weC Mote (30 produced) • Rene Mote (850 produced) • Dot (1000 produce) • Mica node (current, 1800 produced) • Time warp accelerator for MICA • Silicon prototype ? NEC Arch

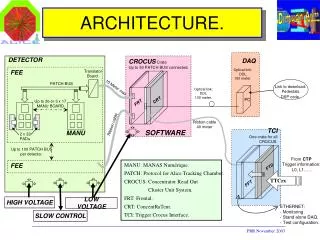

Application Controller RF Transceiver Node Communication Architecture Classic Protocol Processor Direct Device Control Hybrid Accelerator NEC Arch

Novel Protocol Examples • Low-power Listening • Really Tight Application-level Time Synchronization • Localization • Wake-up • MACs • Self-organization NEC Arch

Low-Power Listening • Costs about as much to listen as to xmit, even when nothing is received • Must turn radio off when there is nothing to hear. • Time-slotting and rendezvous cost BW and Latency • Can turn radio on/of in <1 bit • Small sub-msg recv sampling • Trade small, infrequent tx cost for freq. Rx savings NEC Arch

Exposing Time Synchronization Up • Many applications require correlated data sampling • Distributed time sync accuracy bounded by ½ the variance in RTT. • Successful radio transmission requires sub-bit synchronization • Provide accurate timestamping with msg delivery • Jitter < 0.1us (propagation) + 0.25 us (edge capture accuracy) + 0.625 us (clock synch) NEC Arch

Error Error Noise Noise Localization • Many applications need to derive physical placement from observations • Spatial sampling, proximity, context-awareness • Radio is another sensor • Sample baseband to estimate distance • Need a lot of statistical data • Calibration and multiple-observations are key • Acoustic time-of-flight alternative • Requires good time synchronization NEC Arch

narrow standardized intrerface rich physical interface New Architectures? Embedded Network Arch. Typical Wireless Arch. (cellphone) • Traditional approach is to partition design into specialized subsystems with rigid interfaces. • TinyOS allows low and high-level processing to be interleaved. • rich physical information can be exposed • specialized hardware to accelerate primitives • Enables cross-layer optimizations audio kbd / display Sensor / Actuators Codec Application Controller CoProc Multi-Purpose Controller DSP protocol accelerators Protocol Processor RF Transceiver RF Transceiver NEC Arch

First Silicon Goals • Continue trend of building and evaluating • Goal is to build something to get momentum • Learn “economics of silicon” • RF Accelerator designed as mica add-on • Increase RF transmission speed and reliability while decreasing CPU involvement NEC Arch

Capabilities • RF Communication Support • Start Symbol Detection • Signal clock extraction and continual resynchronization • Transmission and reception buffering to relax CPU real-time constraints • Energy Consumption • 1 Mbps (> 100 uA) • Mote Requires approximately 3mA of CPU. NEC Arch

“Mote Chip” Goals • Replicate and extend the functionality of the MICA • Decrease size of node to cubic millimeters • Reduce cost to <$1 • Include AVR-like* Core, ADC, RF Communication Support, UART, SPI, RAM, Radio, Timing modules • Target shortcoming of COTS capabilities NEC Arch

Silicon TinyOS Support NEC Arch

Communication Interface • Hardware provides ‘AM’ interface • Same functionality originally implemented in hardware • Hardware handles • Message send command with TOSMsgPtr • Hardware signals • Message arrival event with TOSMsgPtr • CPU communication overhead dropped from approx. 2MIPS down to 0. NEC Arch

Xilinx XCV2000E 2.5 million gates – 10x the size of an AVR core Also has… Ethernet A/V Encoder Compact Flash Internal and External RAM Mode Chip experimental setup NEC Arch

First Prototype 2mm • IO Pads • RAM blocks • MMU logic • Debug logic • ADC • CPU Core • RF Place Holder Core Area only 50% full… NEC Arch

Chip Area Breakdown • 3K RAM = 1.5 mm2 • CPU Core = 1mm2 • RF COMM stack = .5mm2 • RADIO = .25 mm2 • ADC 1/64 mm2 • I/O PADS NEC Arch

Core Area Breakdown NEC Arch

External Components Required • Current Prototype • 2 External clock generators • 1 External radio • Power source • End Goal • 1 External Inductor (RF oscillation) • 1 External Crystal (time keeping) • Power source NEC Arch

Example: monitoring and alarm • Monitoring • sample every 4 seconds, aggregate over 5 minutes, transmit statistical summary • ~20,000 samples, ~300 reports per day per node • aggregate statistics up the routing tree • schedule rendezvous, so radio mostly off • Alarm • upon detection of dramatic environmental change • routes alarm through parent at any time • Where the energy goes • sleeping • sensing & processing • communication • listening for communication to start • listening for an alarm message NEC Arch

Cross-Layer optimization • Sensing & Processing • 15 mw 17 mJ per day • Sleeping • 45 uw 5038 mJ per day • Communination • hardware accelerators for edge capture and serialization • 10 kbps => 50 kbps 2262 => 452 mJ/day5x • Rendezvous: 2x time-synchronization* • time-stamp packets: +- 100 ms • radio bit edge detection: +- 2 us • radio-level timesynch 669 => 33 mj/day20x • Wake-up • packet listen: 108 ms (21 ms) 54,000 => 25 mj/day2000x • sample radio channel for energy: 50 us • Combined: 2AA lifetime grows from 1 year to 9 years • dominated by sleep energy * receiver-based alternative (Elison) NEC Arch

What integration buys... • 3K RAM = 1.5 mm2 • CPU Core = 1mm2 • RF COMM stack = .5mm2 • RADIO = .25 mm2 • ADC 1/64 mm2 • I/O PADS • Expected sleep: 1 uW • 400+ years on AA • 4 Mhz < 1 mW • Radio: • .5mm2, -90dBm receive sensitivity • 1 mW power at 100Kbps • ADC: • 20 pJ/sample • 10 Ksamps/second = .2 uW. RAM mmu ADC Proc Radio (tbd) NEC Arch