Real Examples and Key Points of Virtual Memory in OS

Understand virtual memory as a cache technique, address mapping via page tables, TLB caches, and effects on memory access. Learn about protection, sharing, and performance in OS virtual memory systems.

Real Examples and Key Points of Virtual Memory in OS

E N D

Presentation Transcript

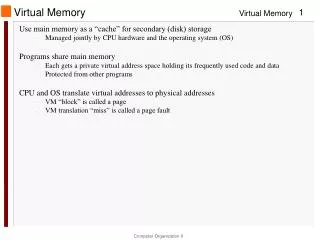

Read 4.10 Virtual Memory Really this is in OS – but We need to see how the OS will interact with the HW Peer Instruction Lecture Materials for Computer ArchitecturebyDr. Leo Porteris licensed under aCreative Commons Attribution-NonCommercial-ShareAlike 3.0 Unported License.

Virtual Memory • It’s just another level in the cache/memory hierarchy • Virtual memoryis the name of the technique that allows us to view main memory as a cache of a larger memory space (on disk). Add latencies 1-4 (L2 – 14) 40-60 150-300 10,000,000-80,000,000 cpu $ cacheing cache cacheing memory virtual memory disk

Virtual Memory • What happens if another program in the processor uses the same addresses that yours does? • What happens if your program uses addresses that don’t exist in the machine? • What happens to “holes” in the address space your program uses? • Can someone else’s program touch your data (or vice versa)?

Virtual Memory Virtual Page Number • is just a mapping function from virtual memory addresses to physical memory locations, which allows cacheing of virtual pages in physical memory. Required because main memory is fully associative. A zero valid bit means…

Virtual Memory mapping virtual addresses physical addresses virtual addresses disk

Address translation via the page table virtual address virtual page number page offset • all page mappings are in the page table, so hit/miss is determined solely by the valid bit (i.e., no tag) physical page number valid page table reg page table physical address physical page number page offset

Virtual Memory • Suppose you have 8 KB pages, a 64 bit byte address, and 512MB of RAM. How many bits are translated (from your virtual page number to your physical page number)?

Address translation via the page table virtual address virtual page number page offset physical page number valid page table reg page table physical address physical page number page offset 8 KB pages, a 64 bit byte address, and 512MB of RAM

Virtual Memory • So far – given what we know about VM, what is the fewest number of accesses to main memory possibly from a single MIPS lw instruction? Write – NO TLB I Page Table lookup I Miss D Page Table Lookup D Miss

Making Address Translation Fast • A cache for address translations: translation lookaside buffer (TLB) A zero valid bit means…

TLBs and caches Block

32-bit virtual addresses, 8 KB pages, 2 GB of RAM. Your cache has 64 byte blocks and is 32 KB in size. You are considering 2-way or 4-way. Your boss says 4-way would have a better hit time – is he right?

8KB page, 2 GB RAM, 2-way vs. 4way 64 byte blocks, 32KB 8KB = 2^13 32KB = 2^15 TLBs and caches Block

Walkthrough the FIRST memory access TLB Miss TLB exception Fill TLB Page fault Call OS to replace the page and update page table Fill TLB with now valid entry Request that physical address Cache miss Cache miss Memory hit Fill Fill

Walkthrough a COMMON memory access TLB hit/translate Cache hit These could potentially Be in parallel

Virtual Memory – Real Examples • OS+Presenter+misc > 650MB • 512MB of RAM Mention WoW example

Virtual Memory Key Points • How does virtual memory provide: • protection? • sharing? • performance? • illusion of large main memory? • Virtual Memory requires twice as many memory accesses, so we cache page table entries in the TLB. • Three things can go wrong on a memory access: cache miss, TLB miss, page fault.